USB on-the-go full-speed (OTG_FS) RM0351

1520/1693 DocID024597 Rev 3

Device-mode CSR map

These registers must be programmed every time the core changes to device mode.

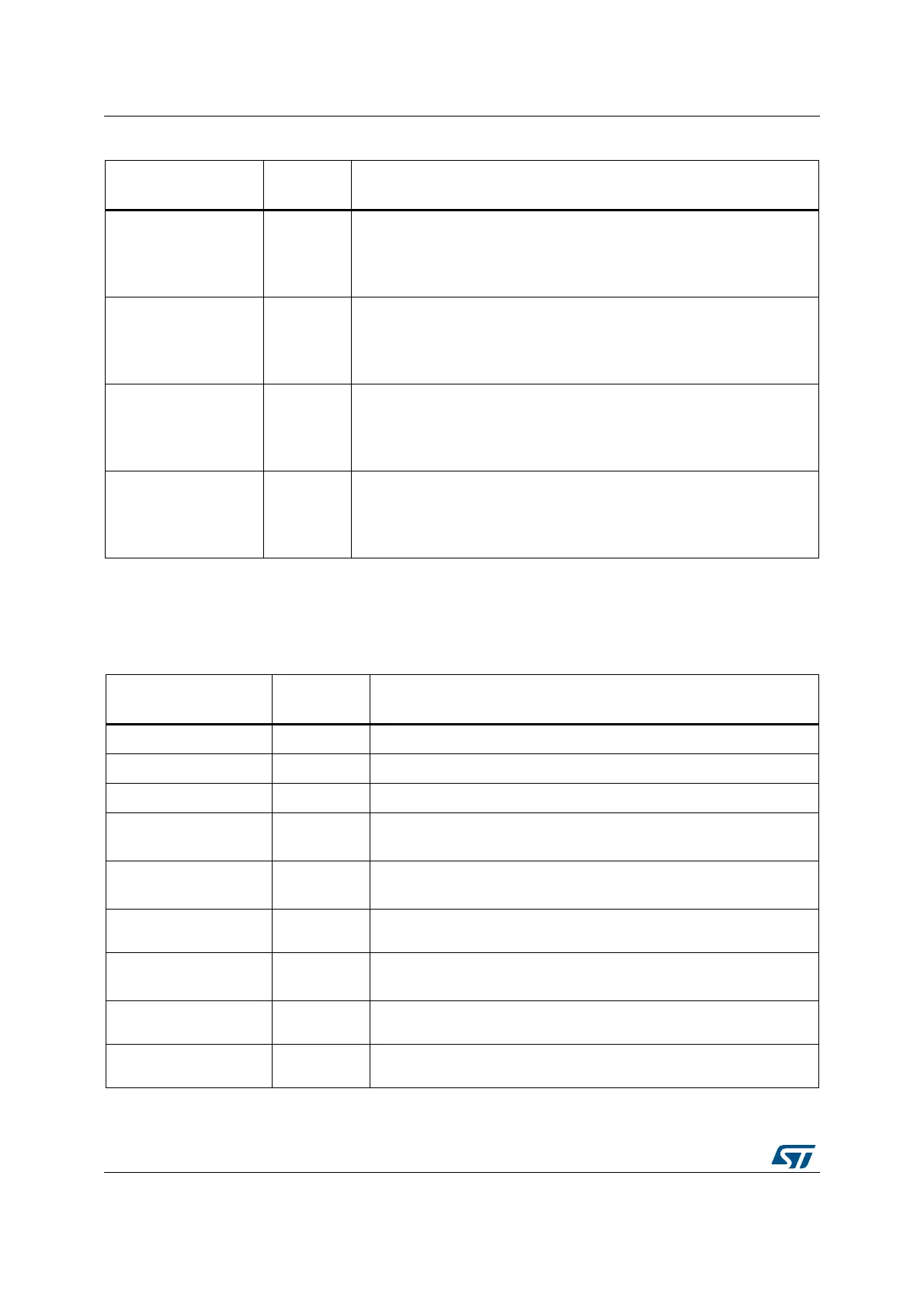

OTG_HCCHARx

0x500

0x520

...

0x660

OTG Host channel-x characteristics register (OTG_HCCHARx) (x = 0..11,

where x = Channel_number) on page 1558

OTG_HCINTx

0x508

0x528

....

0x668

OTG Host channel-x interrupt register (OTG_HCINTx) (x = 0..11, where

x = Channel_number) on page 1560

OTG_HCINTMSKx

0x50C

0x52C

....

0x66C

OTG Host channel-x interrupt mask register (OTG_HCINTMSKx)

(x = 0..11, where x = Channel_number) on page 1561

OTG_HCTSIZx

0x510

0x530

....

0x670

OTG Host channel-x transfer size register (OTG_HCTSIZx) (x = 0..11,

where x = Channel_number) on page 1562

Table 257. Host-mode control and status registers (CSRs) (continued)

Acronym

Offset

address

Register name

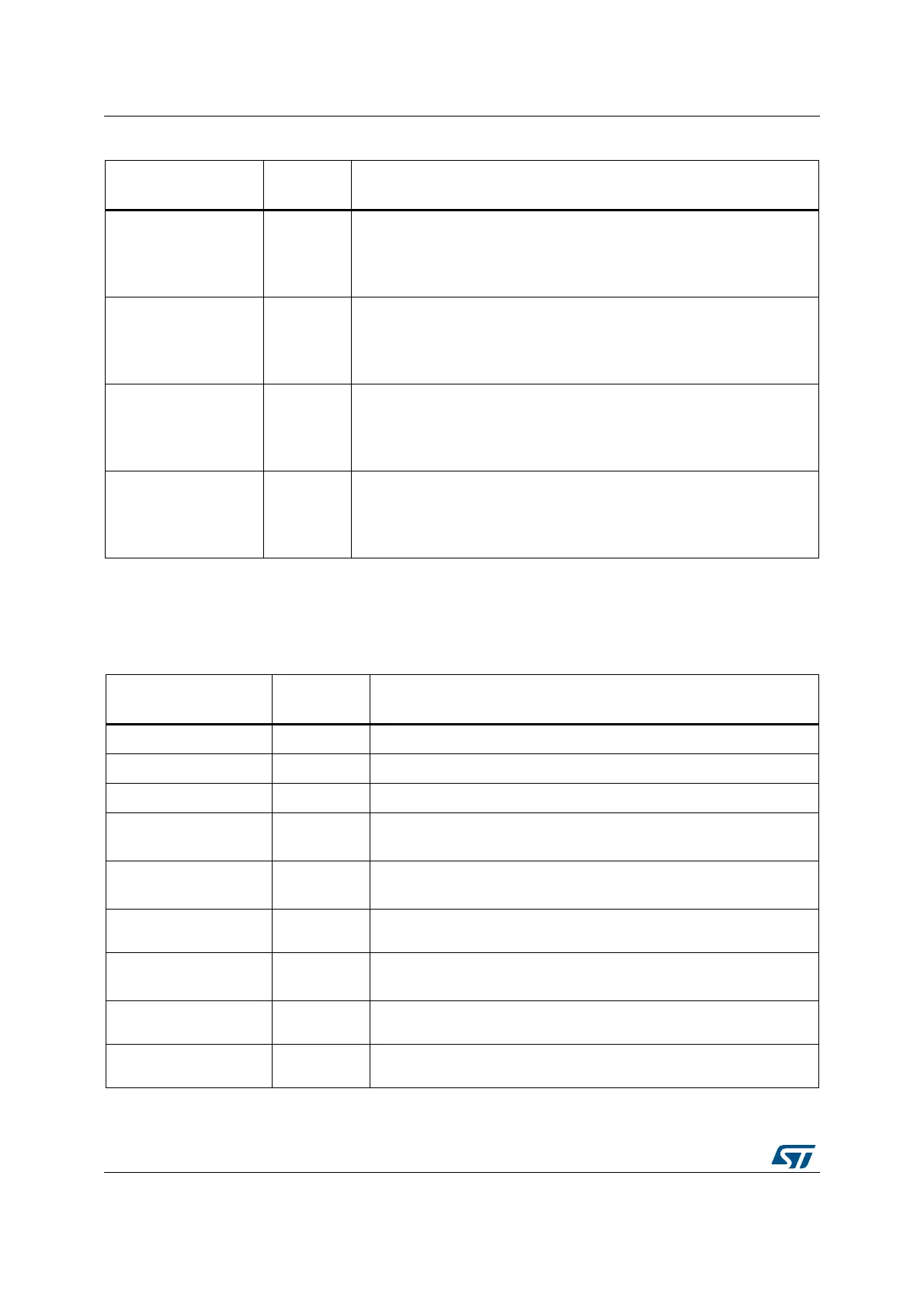

Table 258. Device-mode control and status registers

Acronym

Offset

address

Register name

OTG_DCFG 0x800 OTG device configuration register (OTG_DCFG) on page 1563

OTG_DCTL 0x804 OTG device control register (OTG_DCTL) on page 1564

OTG_DSTS 0x808 OTG device status register (OTG_DSTS) on page 1566

OTG_DIEPMSK 0x810

OTG device IN endpoint common interrupt mask register

(OTG_DIEPMSK) on page 1567

OTG_DOEPMSK 0x814

OTG device OUT endpoint common interrupt mask register

(OTG_DOEPMSK) on page 1568

OTG_DAINT 0x818

OTG device all endpoints interrupt register (OTG_DAINT) on

page 1568

OTG_DAINTMSK 0x81C

OTG all endpoints interrupt mask register (OTG_DAINTMSK) on

page 1569

OTG_DVBUSDIS 0x828

OTG device VBUS discharge time register (OTG_DVBUSDIS) on

page 1570

OTG_DVBUSPULSE 0x82C

OTG device VBUS pulsing time register (OTG_DVBUSPULSE) on

page 1570

Loading...

Loading...