USB on-the-go full-speed (OTG_FS) RM0351

1560/1693 DocID024597 Rev 3

43.15.28 OTG Host channel-x interrupt register (OTG_HCINTx)

(x = 0..11, where x = Channel_number)

Address offset: 0x508 + (Channel_number × 0x20)

Reset value: 0x0000 0000

This register indicates the status of a channel with respect to USB- and AHB-related events.

It is shown in Figure 501. The application must read this register when the host channels

interrupt bit in the Core interrupt register (HCINT bit in OTG_GINTSTS) is set. Before the

application can read this register, it must first read the host all channels interrupt

(OTG_HAINT) register to get the exact channel number for the host channel-x interrupt

register. The application must clear the appropriate bit in this register to clear the

corresponding bits in the OTG_HAINT and OTG_GINTSTS registers.

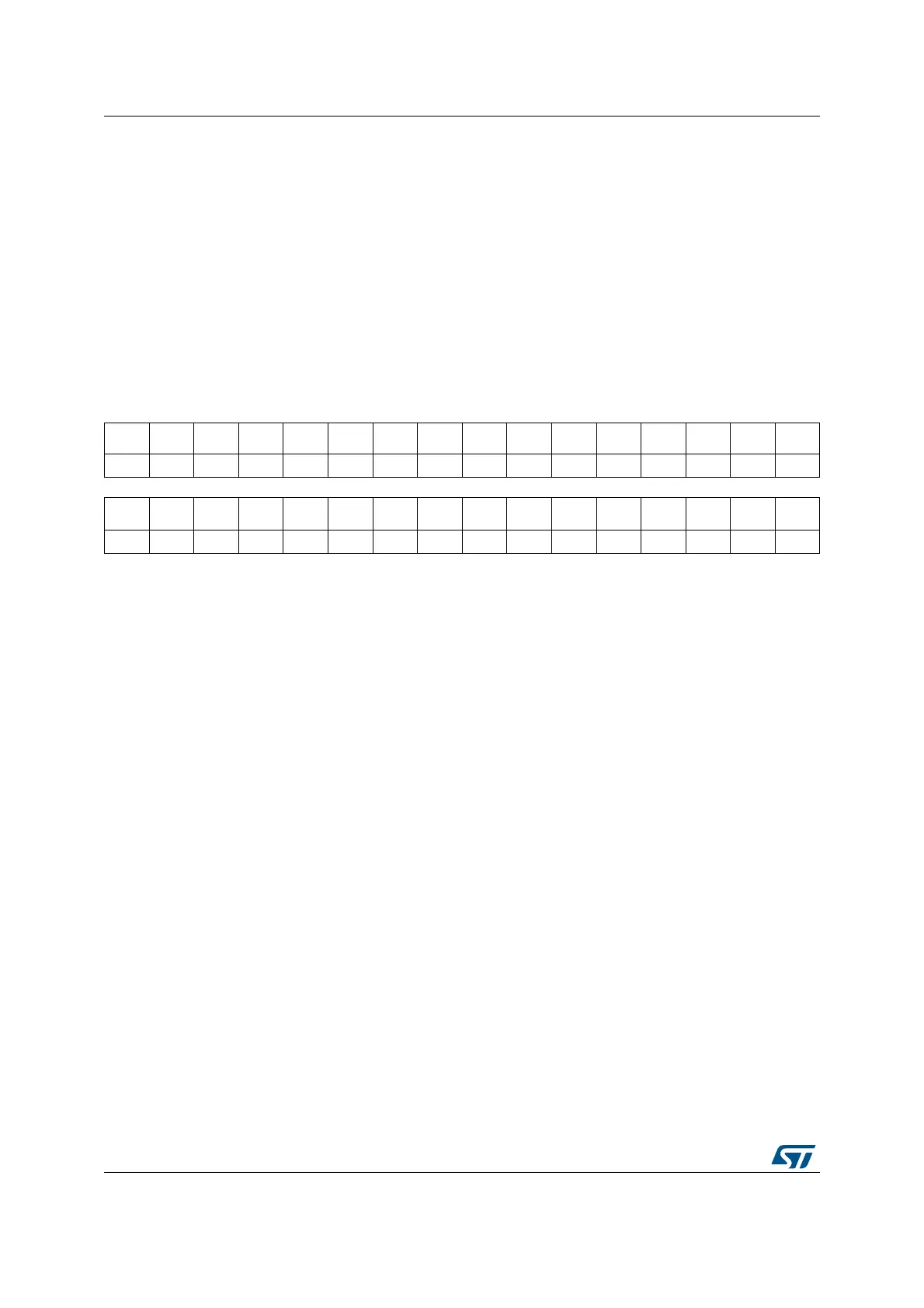

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. DTERR

FRM

OR

BBERR TXERR Res. ACK NAK STALL Res. CHH XFRC

rc_w1rc_w1rc_w1rc_w1 rc_w1rc_w1rc_w1 rc_w1rc_w1

Bits 31:11 Reserved, must be kept at reset value.

Bit 10 DTERR: Data toggle error

Bit 9 FRMOR: Frame overrun

Bit 8 BBERR: Babble error

Bit 7 TXERR: Transaction error

Indicates one of the following errors occurred on the USB.

CRC check failure

Timeout

Bit stuff error

False EOP

Bit 6 Reserved, must be kept at reset value for USB OTG FS.

Bit 5 ACK: ACK response received/transmitted interrupt

Bit 4 NAK: NAK response received interrupt

Bit 3 STALL: STALL response received interrupt

Bit 2 Reserved, must be kept at reset value for USB OTG FS.

Bit 1 CHH: Channel halted

Indicates the transfer completed abnormally either because of any USB transaction error or

in response to disable request by the application.

Bit 0 XFRC: Transfer completed

Transfer completed normally without any errors.

Loading...

Loading...