Analog-to-digital converters (ADC) RM0351

496/1693 DocID024597 Rev 3

regular simultaneous mode when MDMA=0b00).

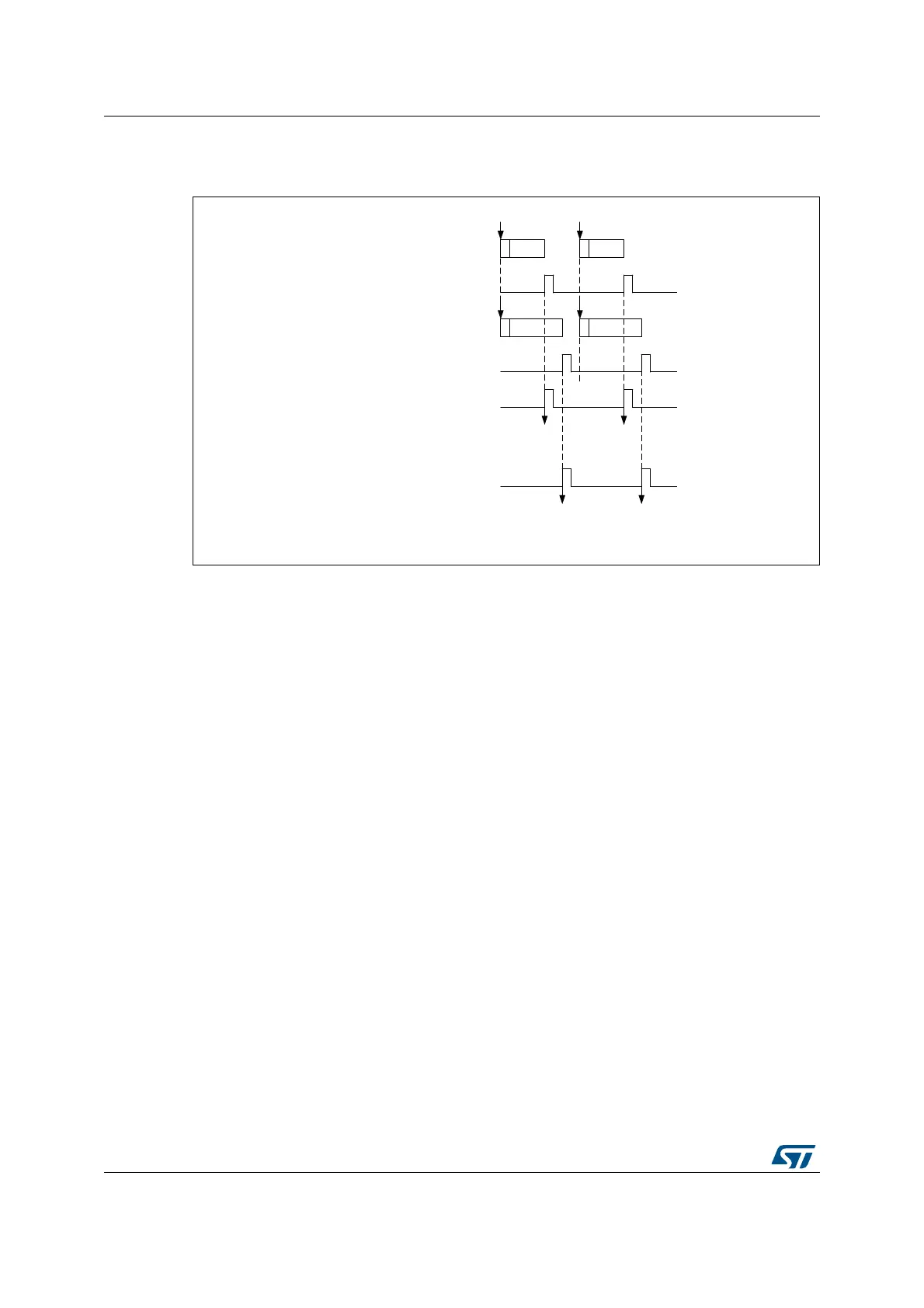

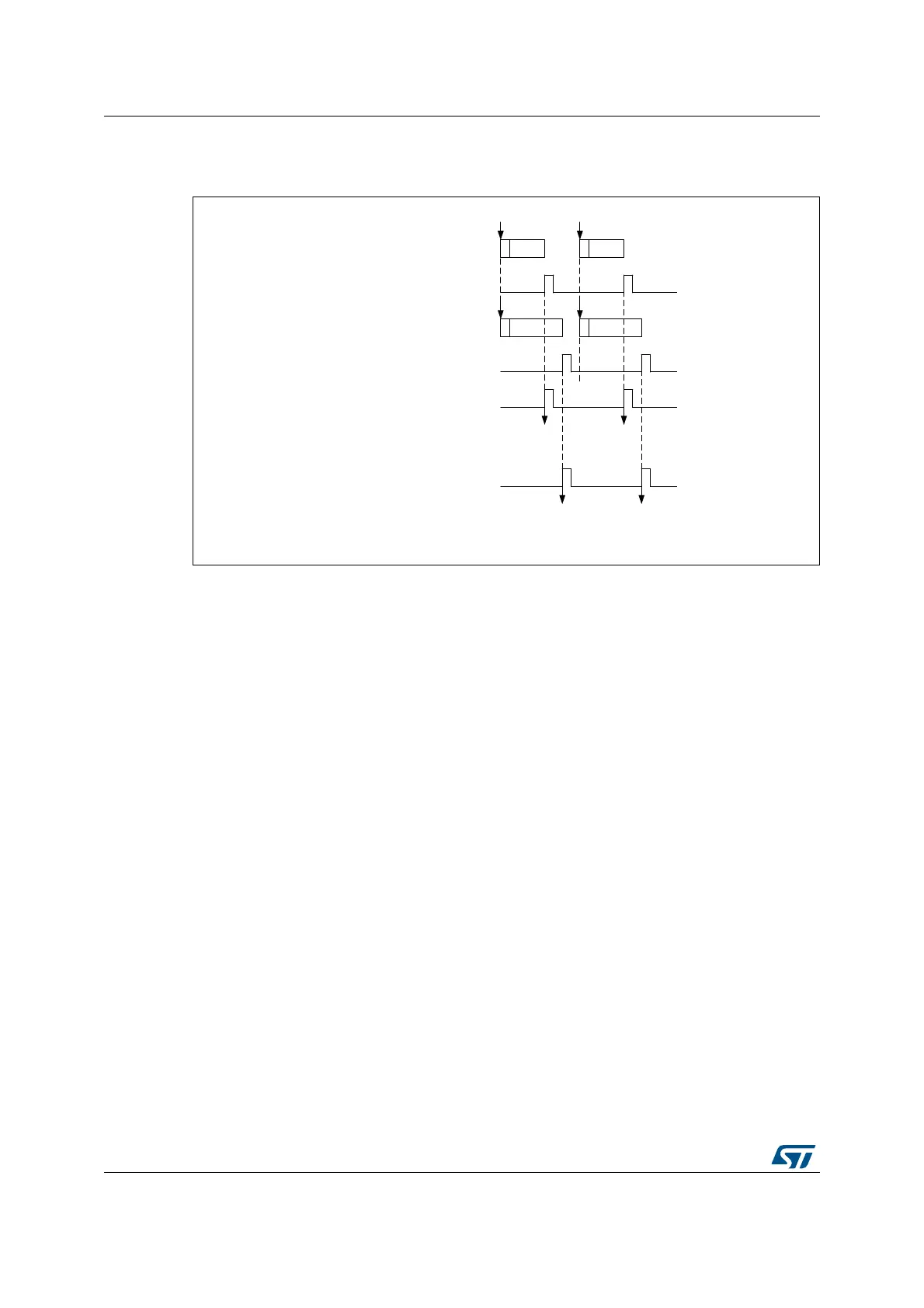

Figure 123. DMA Requests in regular simultaneous mode when MDMA=0b00

In simultaneous regular and interleaved modes, it is also possible to save one DMA channel

and transfer both data using a single DMA channel. For this MDMA bits must be configured

in the ADCx_CCR register:

• MDMA=0b10: A single DMA request is generated each time both master and slave

EOC events have occurred. At that time, two data items are available and the 32-bit

register ADCx_CDR contains the two half-words representing two ADC-converted data

items. The slave ADC data take the upper half-word and the master ADC data take the

lower half-word.

This mode is used in interleaved mode and in regular simultaneous mode when

resolution is 10-bit or 12-bit.

Example:

Interleaved dual mode: a DMA request is generated each time 2 data items are

available:

1st DMA request: ADCx_CDR[31:0] = SLV_ADCx_DR[15:0] |

MST_ADCx_DR[15:0]

2nd DMA request: ADCx_CDR[31:0] = SLV_ADCx_DR[15:0] |

MST_ADCx_DR[15:0]

06Y9

&+$'&0DVWHUUHJXODU

&+

7ULJJHU 7ULJJHU

&+

&+

&RQILJXUDWLRQZKHUHHDFKVHTXHQFHFRQWDLQVRQO\RQHFRQYHUVLRQ

$'&0DVWHU(2&

$'&6ODYHUHJXODU

$'&6ODYH(2&

'0$UHTXHVWIURP$'&0DVWHU

'0$UHTXHVWIURP$'&6ODYH

'0$UHDGV0DVWHU

$'&B'5

'0$UHDGV0DWHU

$'&B'5

'0$UHDGV6ODYH

$'&B'5

'0$UHDGV6ODYH

$'&B'5

Loading...

Loading...