DocID024597 Rev 3 213/1693

RM0351 Reset and clock control (RCC)

253

6.4.8 Clock interrupt flag register (RCC_CIFR)

Address offset: 0x1C

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

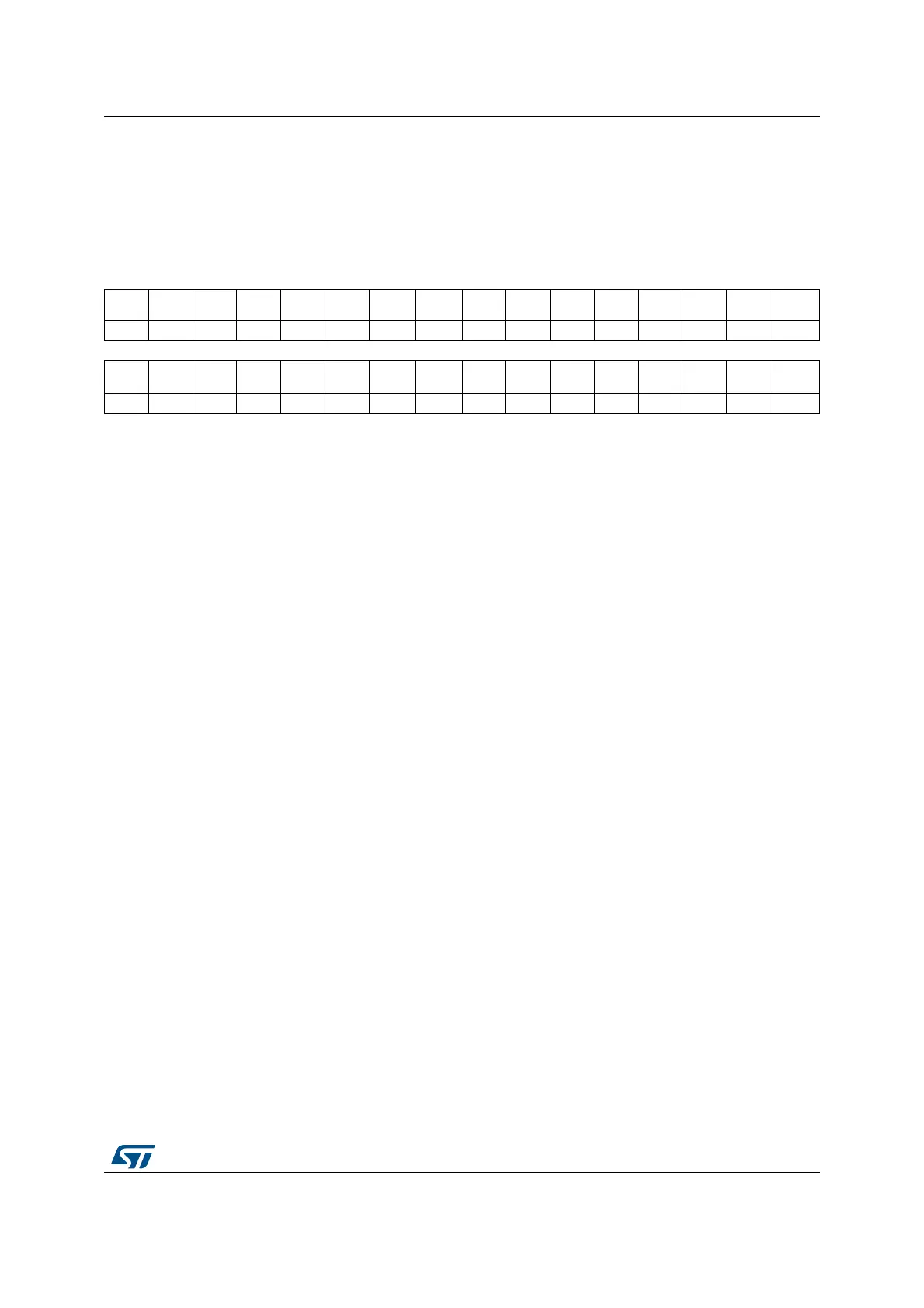

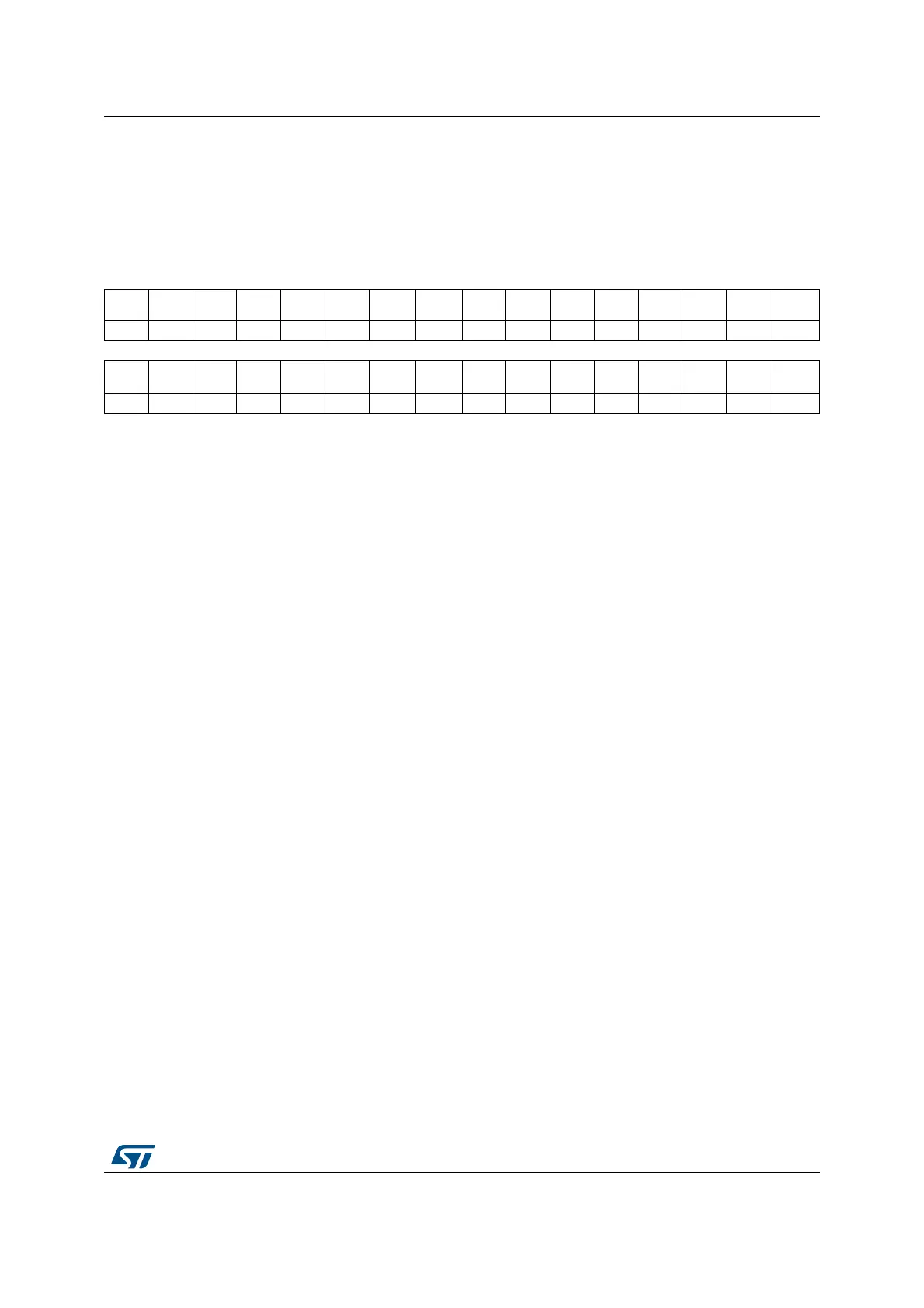

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8765432 1 0

Res. Res. Res. Res. Res. Res.

LSE

CSSF

CSSF

PLLSAI

2RDYF

PLLSAI

1RDYF

PLL

RDYF

HSE

RDYF

HSI

RDYF

MSI

RDYF

LSE

RDYF

LSI

RDYF

r r rrrrrr r r

Bits 31:10 Reserved, must be kept at reset value.

Bit 9 LSECSSF: LSE Clock security system interrupt flag

Set by hardware when a failure is detected in the LSE oscillator.

Cleared by software setting the LSECSSC bit.

0: No clock security interrupt caused by LSE clock failure

1: Clock security interrupt caused by LSE clock failure

Bit 8 CSSF: Clock security system interrupt flag

Set by hardware when a failure is detected in the HSE oscillator.

Cleared by software setting the CSSC bit.

0: No clock security interrupt caused by HSE clock failure

1: Clock security interrupt caused by HSE clock failure

Bit 7 PLLSAI2RDYF: PLLSAI2 ready interrupt flag

Set by hardware when the PLLSAI2 locks and PLLSAI2RDYDIE is set.

Cleared by software setting the PLLSAI2RDYC bit.

0: No clock ready interrupt caused by PLLSAI2 lock

1: Clock ready interrupt caused by PLLSAI2 lock

Bit 6 PLLSAI1RDYF: PLLSAI1 ready interrupt flag

Set by hardware when the PLLSAI1 locks and PLLSAI1RDYDIE is set.

Cleared by software setting the PLLSAI1RDYC bit.

0: No clock ready interrupt caused by PLLSAI1 lock

1: Clock ready interrupt caused by PLLSAI1 lock

Bit 5 PLLRDYF: PLL ready interrupt flag

Set by hardware when the PLL locks and PLLRDYDIE is set.

Cleared by software setting the PLLRDYC bit.

0: No clock ready interrupt caused by PLL lock

1: Clock ready interrupt caused by PLL lock

Bit 4 HSERDYF: HSE ready interrupt flag

Set by hardware when the HSE clock becomes stable and HSERDYDIE is set.

Cleared by software setting the HSERDYC bit.

0: No clock ready interrupt caused by the HSE oscillator

1: Clock ready interrupt caused by the HSE oscillator

Loading...

Loading...