DocID024597 Rev 3 1035/1693

RM0351 Low-power timer (LPTIM)

1045

30.7 LPTIM registers

30.7.1 LPTIM interrupt and status register (LPTIMx_ISR)

Address offset: 0x00

Reset value: 0x0000 0000

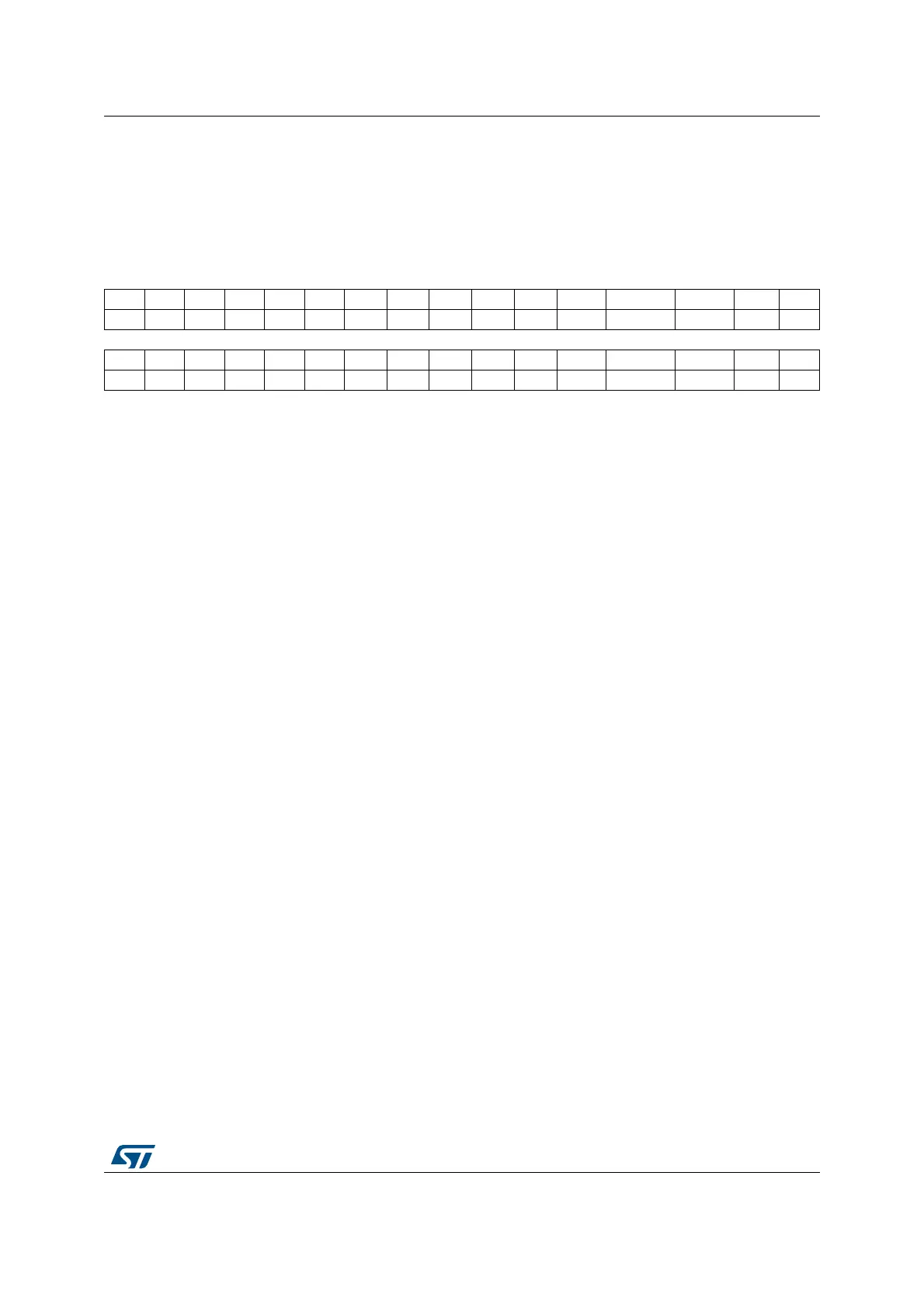

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. DOWN UP ARROK CMPOK EXTTRIG ARRM CMPM

rr r r r rr

Bits 31:7 Reserved, must be kept at reset value.

Bit 6 DOWN: Counter direction change up to down

In Encoder mode, DOWN bit is set by hardware to inform application that the counter direction has

changed from up to down.

Bit 5 UP: Counter direction change down to up

In Encoder mode, UP bit is set by hardware to inform application that the counter direction has

changed from down to up.

Bit 4 ARROK: Autoreload register update OK

ARROK is set by hardware to inform application that the APB bus write operation to the LPTIMx_ARR

register has been successfully completed. If so, a new one can be initiated.

Bit 3 CMPOK: Compare register update OK

CMPOK is set by hardware to inform application that the APB bus write operation to the LPTIMx_CMP

register has been successfully completed. If so, a new one can be initiated.

Bit 2 EXTTRIG: External trigger edge event

EXTTRIG is set by hardware to inform application that a valid edge on the selected external trigger

input has occurred. If the trigger is ignored because the timer has already started, then this flag is not

set.

Bit 1 ARRM: Autoreload match

ARRM is set by hardware to inform application that LPTIMx_CNT register’s value reached the

LPTIMx_ARR register’s value.

Bit 0 CMPM: Compare match

The CMPM bit is set by hardware to inform application that LPTIMx_CNT register value reached the

LPTIMx_CMP register’s value.

Loading...

Loading...