DocID024597 Rev 3 519/1693

RM0351 Analog-to-digital converters (ADC)

540

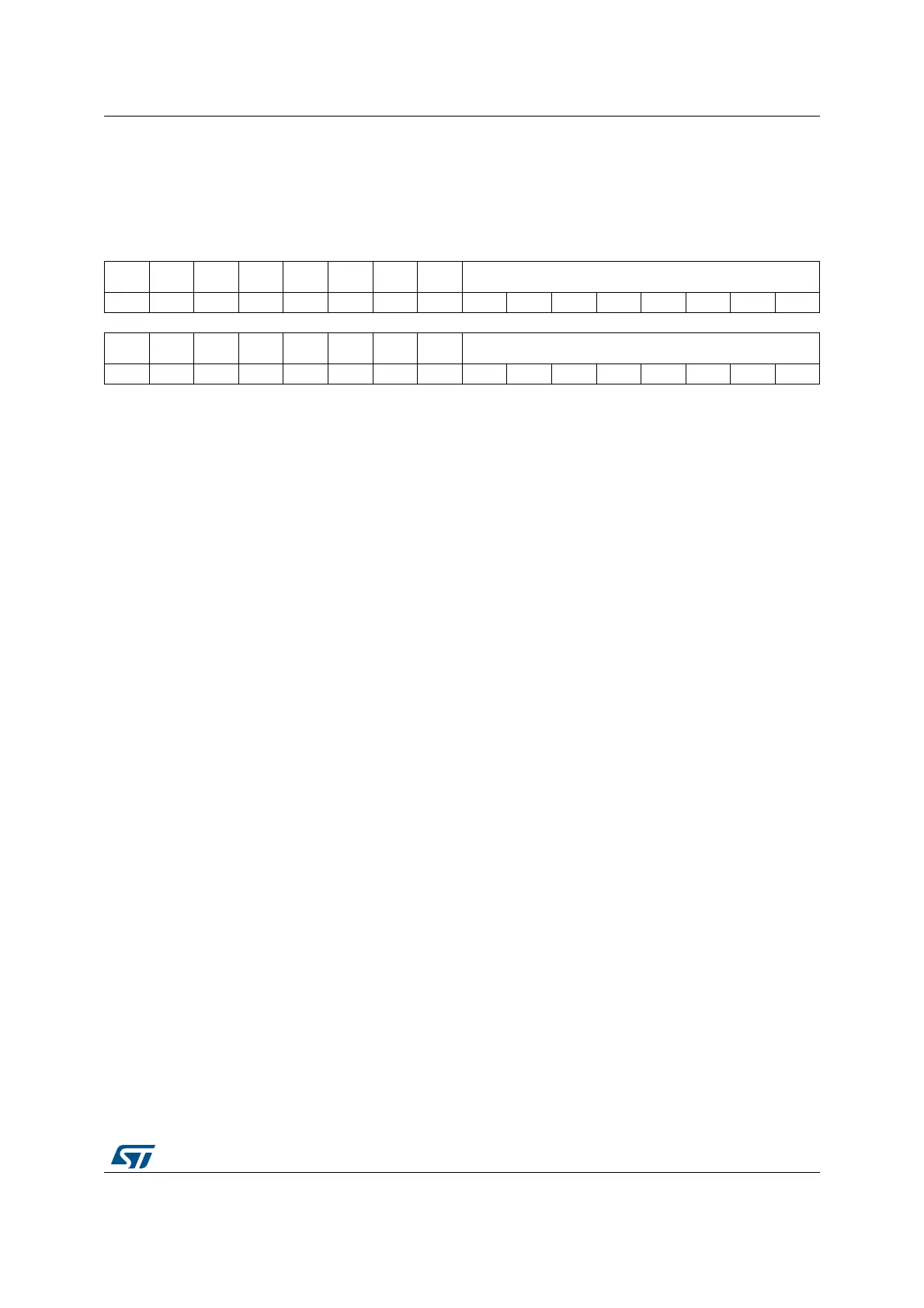

16.5.10 ADC watchdog threshold register 3 (ADCx_TR3)

Address offset: 0x28

Reset value: 0x00FF 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. HT3[7:0]

rw rw rw rw rw rw rw rw

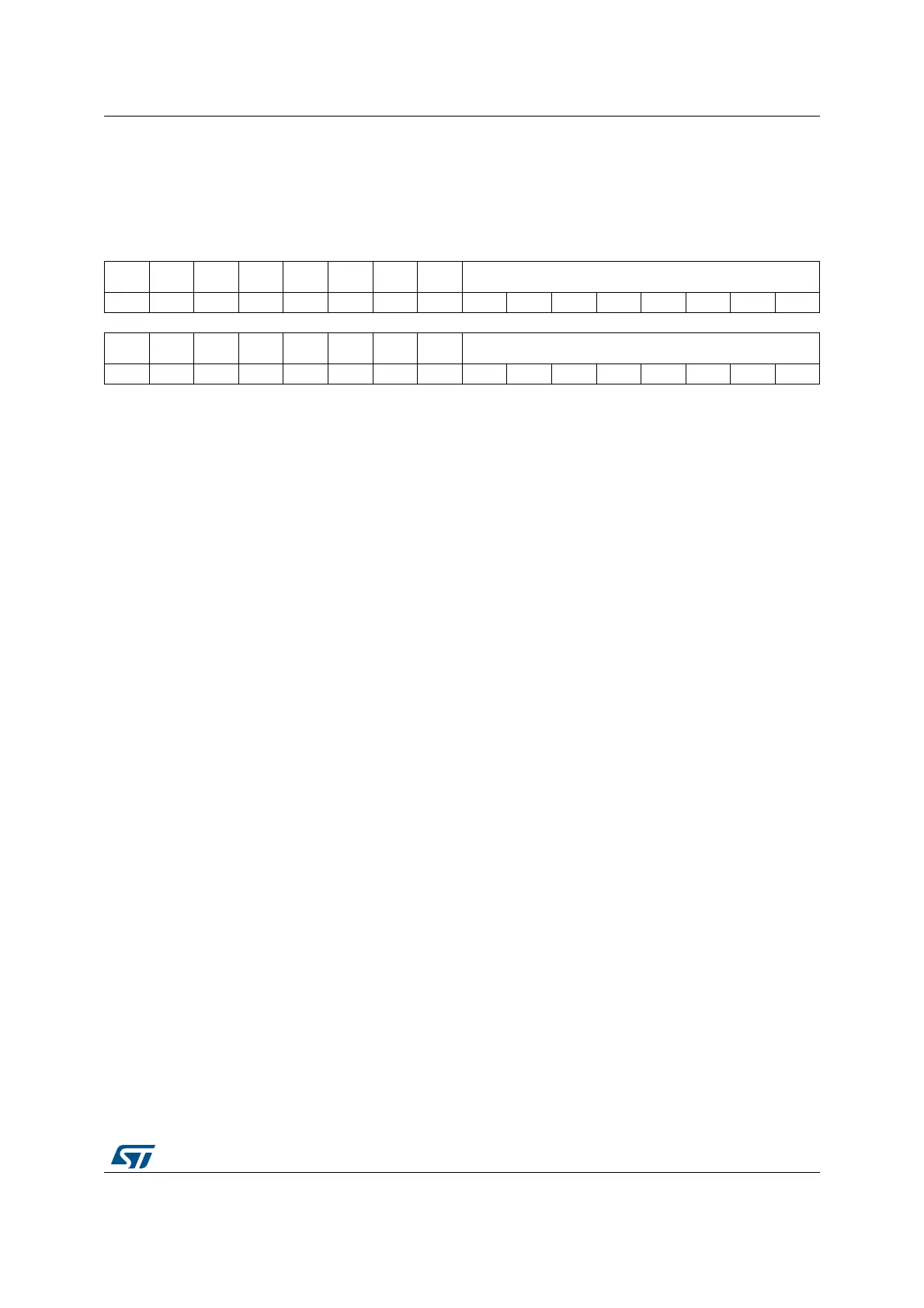

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. LT3[7:0]

rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bits 23:16 HT3[7:0]: Analog watchdog 3 higher threshold

These bits are written by software to define the higher threshold for the analog watchdog 3.

Refer to Section 16.3.28: Analog window watchdog (AWD1EN, JAWD1EN, AWD1SGL, AWD1CH,

AWD2CH, AWD3CH, AWD_HTx, AWD_LTx, AWDx)

Note: Software is allowed to write these bits only when ADSTART=0 and JADSTART=0 (which

ensures that no conversion is ongoing).

Bits 15:8 Reserved, must be kept at reset value.

Bits 7:0 LT3[7:0]: Analog watchdog 3 lower threshold

These bits are written by software to define the lower threshold for the analog watchdog 3.

This watchdog compares the 8-bit of LT3 with the 8 MSB of the converted data.

Note: Software is allowed to write these bits only when ADSTART=0 and JADSTART=0 (which

ensures that no conversion is ongoing).

Loading...

Loading...