Inter-integrated circuit (I2C) interface RM0351

1146/1693 DocID024597 Rev 3

Caution: Changing the TIMEOUTA[11:0] bits and TIDLE bit configuration is not allowed when the

TIMEOUTEN bit is set.

• t

LOW:SEXT

and t

LOW:MEXT

check

Depending on if the peripheral is configured as a master or as a slave, The 12-bit

TIMEOUTB timer must be configured in order to check t

LOW:SEXT

for a slave and

t

LOW:MEXT

for a master. As the standard specifies only a maximum, the user can choose

the same value for the both.

Then the timer is enabled by setting the TEXTEN bit in the I2C_TIMEOUTR register.

If the SMBus peripheral performs a cumulative SCL stretch for a time greater than

(TIMEOUTB+1) x 2048 x t

I2CCLK

, and in the timeout interval described in Bus idle

detection on page 1144 section, the TIMEOUT flag is set in the I2C_ISR register.

Refer to Table 186: Examples of TIMEOUTB settings for various I2CCLK frequencies

Caution: Changing the TIMEOUTB configuration is not allowed when the TEXTEN bit is set.

Bus Idle detection

In order to enable the t

IDLE

check, the 12-bit TIMEOUTA[11:0] field must be programmed

with the timer reload value in order to obtain the t

IDLE

parameter. The TIDLE bit must be

configured to ‘1 in order to detect both SCL and SDA high level timeout.

Then the timer is enabled by setting the TIMOUTEN bit in the I2C_TIMEOUTR register.

If both the SCL and SDA lines remain high for a time greater than (TIMEOUTA+1) x 4 x

t

I2CCLK

, the TIMEOUT flag is set in the I2C_ISR register.

Refer to Table 187: Examples of TIMEOUTA settings for various I2CCLK frequencies (max

tIDLE = 50 µs)

Caution: Changing the TIMEOUTA and TIDLE configuration is not allowed when the TIMEOUTEN is

set.

35.4.12 SMBus: I2C_TIMEOUTR register configuration examples

This section is relevant only when SMBus feature is supported. Please refer to Section 35.3:

I2C implementation.

• Configuring the maximum duration of t

TIMEOUT

to 25 ms:

• Configuring the maximum duration of t

LOW:SEXT

and t

LOW:MEXT

to 8 ms:

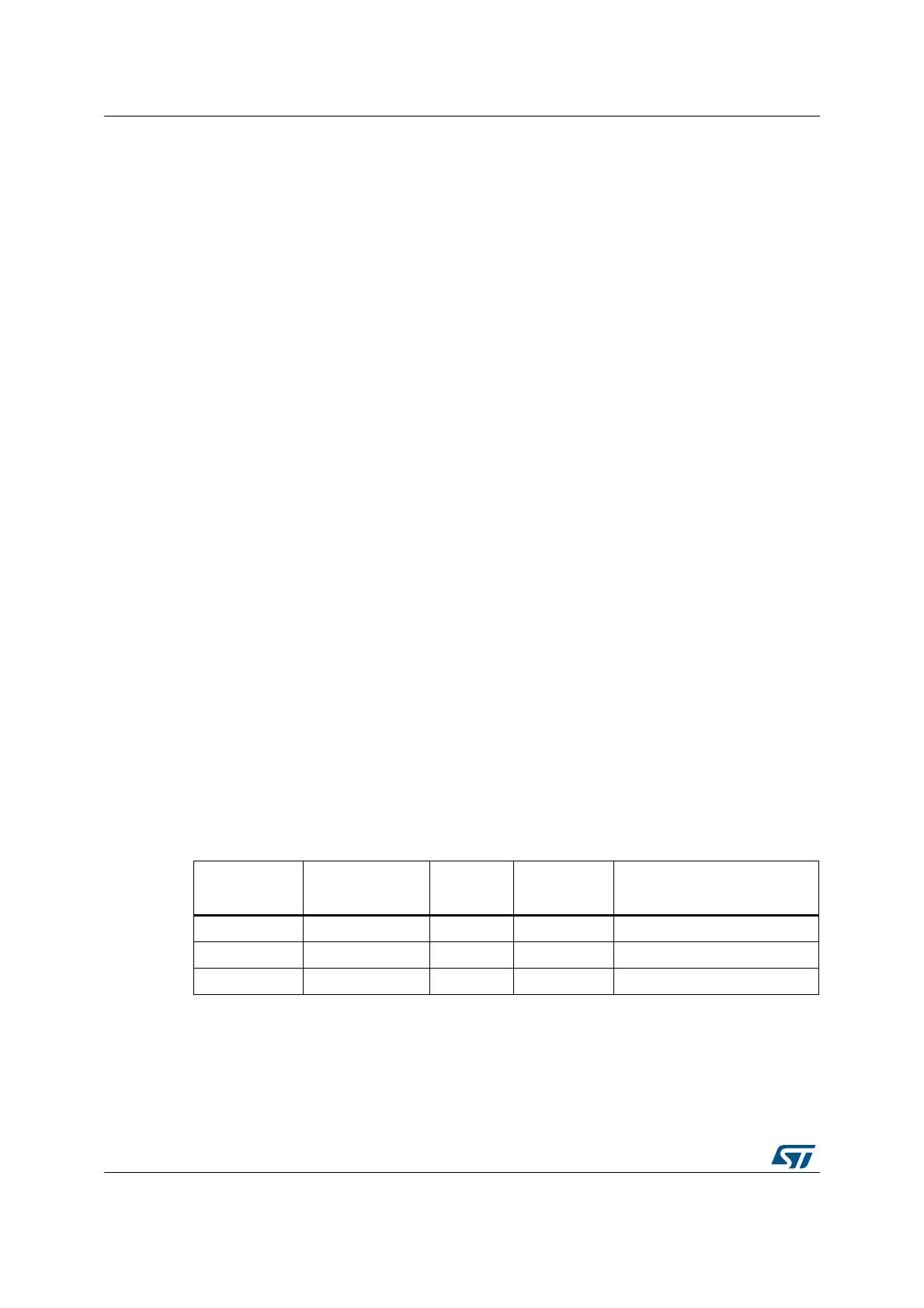

Table 185. Examples of TIMEOUTA settings for various I2CCLK

frequencies

(max t

TIMEOUT

= 25 ms)

f

I2CCLK

TIMEOUTA[11:0]

bits

TIDLE

bit

TIMEOUTEN

bit

t

TIMEOUT

8 MHz 0x61 0 1 98 x 2048 x 125 ns = 25 ms

16 MHz 0xC3 0 1 196 x 2048 x 62.5 ns = 25 ms

48 MHz 0x249 0 1 586 x 2048 x 20.08 ns = 25 ms

Loading...

Loading...