Analog-to-digital converters (ADC) RM0351

502/1693 DocID024597 Rev 3

actual VDDA voltage using the internal reference voltage, resulting in the following formula:

Where:

• VREFINT_CAL is the VREFINT calibration value

• ADCx_DATA is the value measured by the ADC on channel x (right-aligned)

• VREFINT_DATA is the actual VREFINT output value converted by the ADC

• FULL_SCALE is the maximum digital value of the ADC output. For example with 12-bit

resolution, it will be 2

12

- 1 = 4095 or with 8-bit resolution, 2

8

- 1 = 255.

Note: If ADC measurements are done using an output format other than 12 bit right-aligned, all the

parameters must first be converted to a compatible format before the calculation is done.

16.4 ADC interrupts

For each ADC, an interrupt can be generated:

• After ADC power-up, when the ADC is ready (flag ADRDY)

• On the end of any conversion for regular groups (flag EOC)

• On the end of a sequence of conversion for regular groups (flag EOS)

• On the end of any conversion for injected groups (flag JEOC)

• On the end of a sequence of conversion for injected groups (flag JEOS)

• When an analog watchdog detection occurs (flag AWD1, AWD2 and AWD3)

• When the end of sampling phase occurs (flag EOSMP)

• When the data overrun occurs (flag OVR)

• When the injected sequence context queue overflows (flag JQOVF)

Separate interrupt enable bits are available for flexibility.

V

CHANNELx

3.0 V VREFINT_CAL ADCx_DATA××

VREFINT_DATA FULL_SCALE×

--------------------------------------------------------------------------------------------------------

=

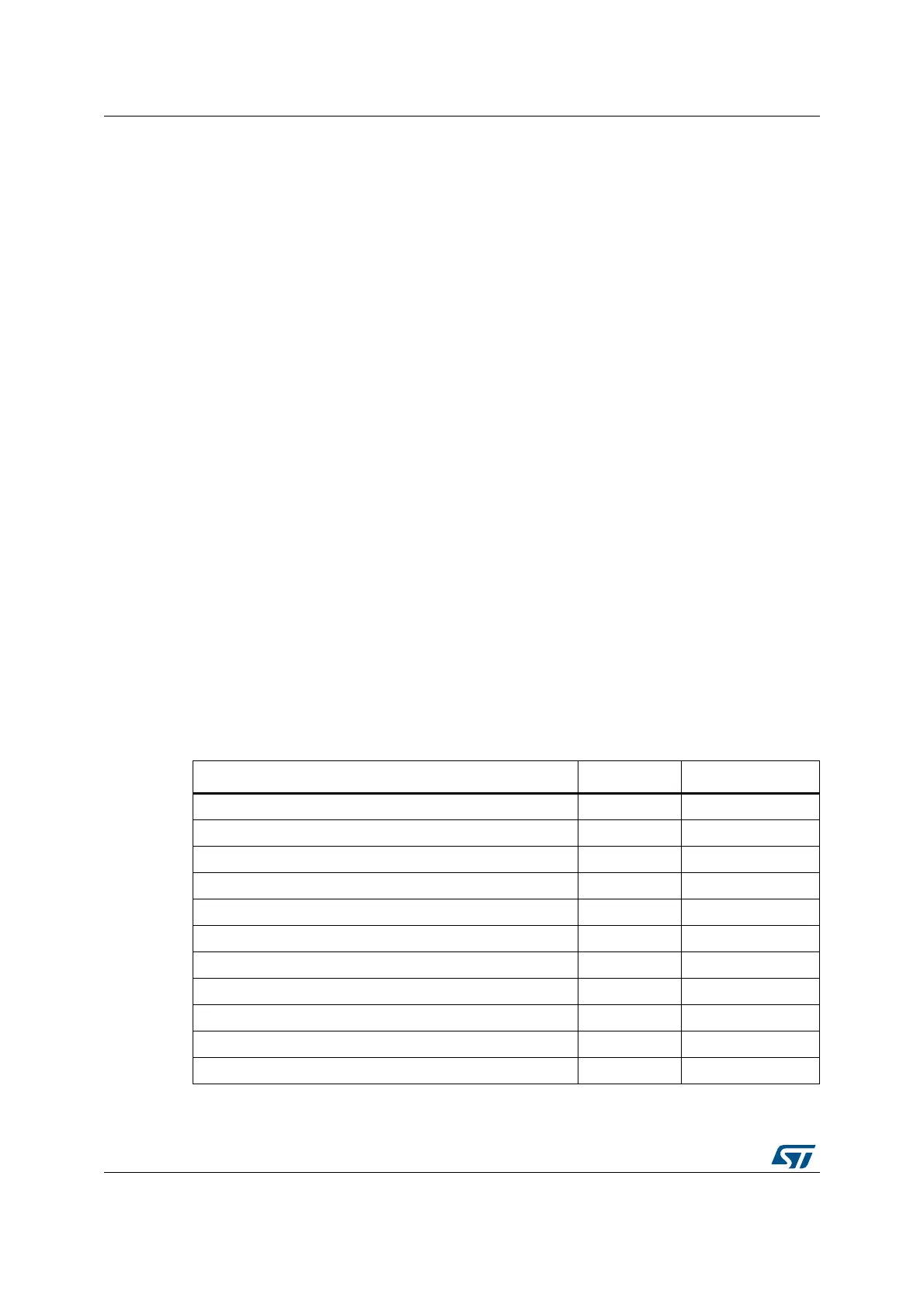

Table 97. ADC interrupts per each ADC

Interrupt event Event flag Enable control bit

ADC ready ADRDY ADRDYIE

End of conversion of a regular group EOC EOCIE

End of sequence of conversions of a regular group EOS EOSIE

End of conversion of a injected group JEOC JEOCIE

End of sequence of conversions of an injected group JEOS JEOSIE

Analog watchdog 1 status bit is set AWD1 AWD1IE

Analog watchdog 2 status bit is set AWD2 AWD2IE

Analog watchdog 3 status bit is set AWD3 AWD3IE

End of sampling phase EOSMP EOSMPIE

Overrun OVR OVRIE

Injected context queue overflows JQOVF JQOVFIE

Loading...

Loading...