SD/SDIO/MMC card host interface (SDMMC) RM0351

1450/1693 DocID024597 Rev 3

Refer to Section 2.2.2: Memory map and register boundary addresses for the register

boundary addresses.

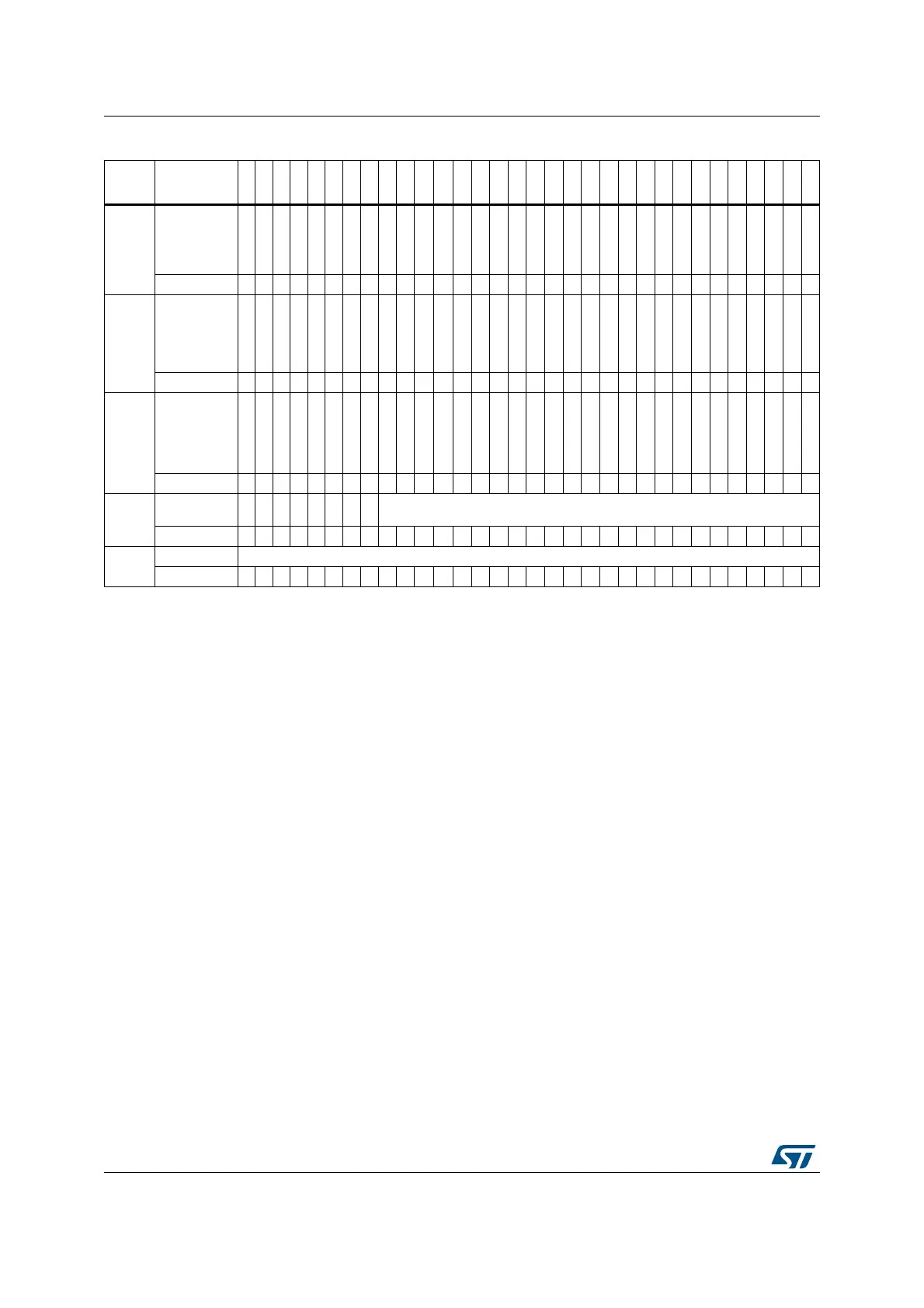

0x34

SDMMC_STA

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

SDIOIT

RXDAVL

TXDAVL

RXFIFOE

TXFIFOE

RXFIFOF

TXFIFOF

RXFIFOHF

TXFIFOHE

RXACT

TXACT

CMDACT

DBCKEND

Res.

DATAEND

CMDSENT

CMDREND

RXOVERR

TXUNDERR

DTIMEOUT

CTIMEOUT

DCRCFAIL

CCRCFAIL

Reset value

00 00000000000 000000000

0x38

SDMMC_ICR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

SDIOITC

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

DBCKENDC

Res.

DATAENDC

CMDSENTC

CMDRENDC

RXOVERRC

TXUNDERRC

DTIMEOUTC

CTIMEOUTC

DCRCFAILC

CCRCFAILC

Reset value

0 0 000000000

0x3C

SDMMC_

MASK

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

SDIOITIE

RXDAVLIE

TXDAVLIE

RXFIFOEIE

TXFIFOEIE

RXFIFOFIE

TXFIFOFIE

RXFIFOHFIE

TXFIFOHEIE

RXACTIE

TXACTIE

CMDACTIE

DBCKENDIE

Res.

DATAENDIE

CMDSENTIE

CMDRENDIE

RXOVERRIE

TXUNDERRIE

DTIMEOUTIE

CTIMEOUTIE

DCRCFAILIE

CCRCFAILIE

Reset value

00 00000000000 000000000

0x48

SDMMC_

FIFOCNT

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

FIFOCOUNT

Reset value

000 000000000000000000000

0x80

SDMMC_FIFO FIF0Data

Reset value

0000000000 0 0 00000000000000000000

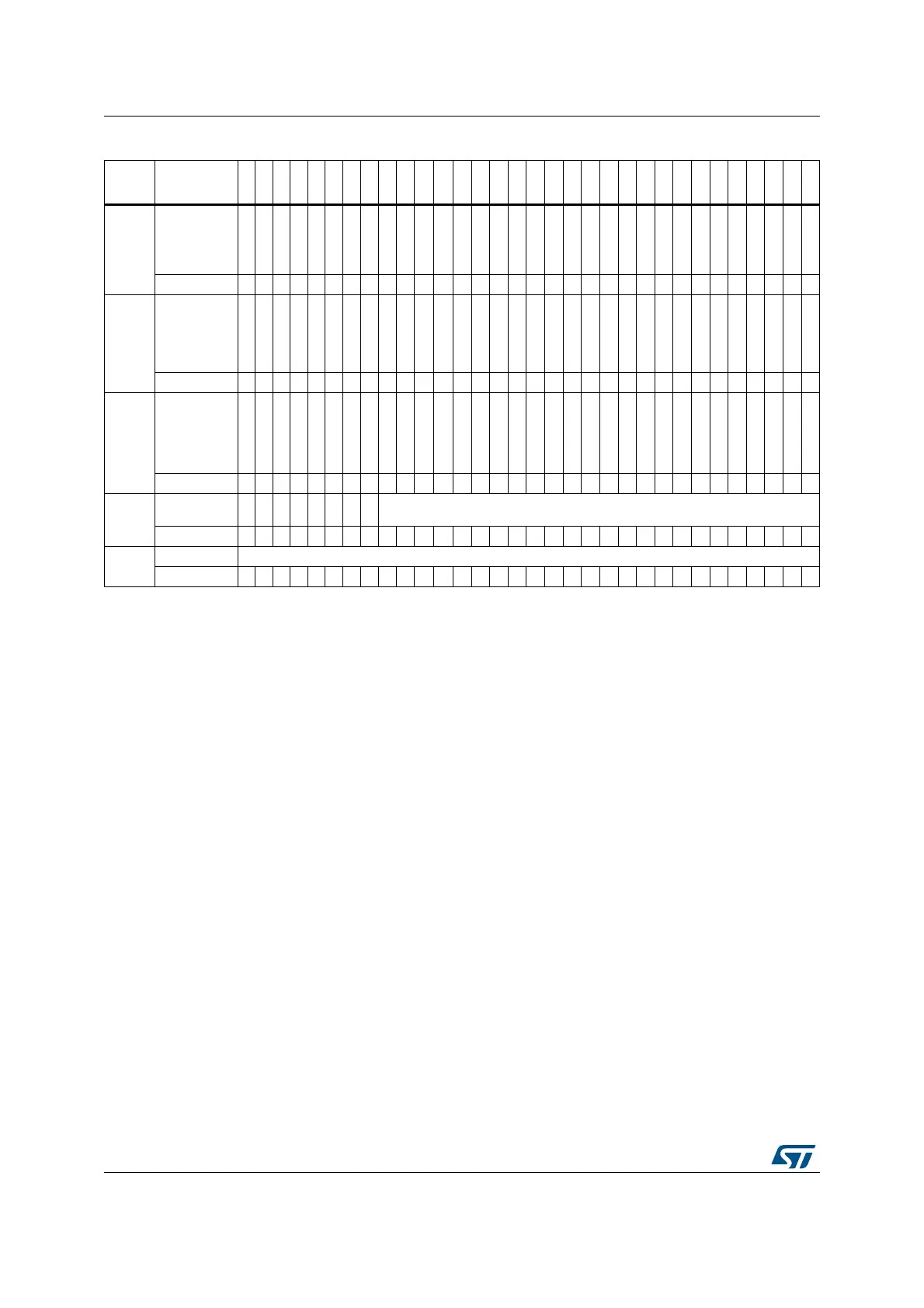

Table 251. SDMMC register map (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...