DocID024597 Rev 3 1479/1693

RM0351 Controller area network (bxCAN)

1494

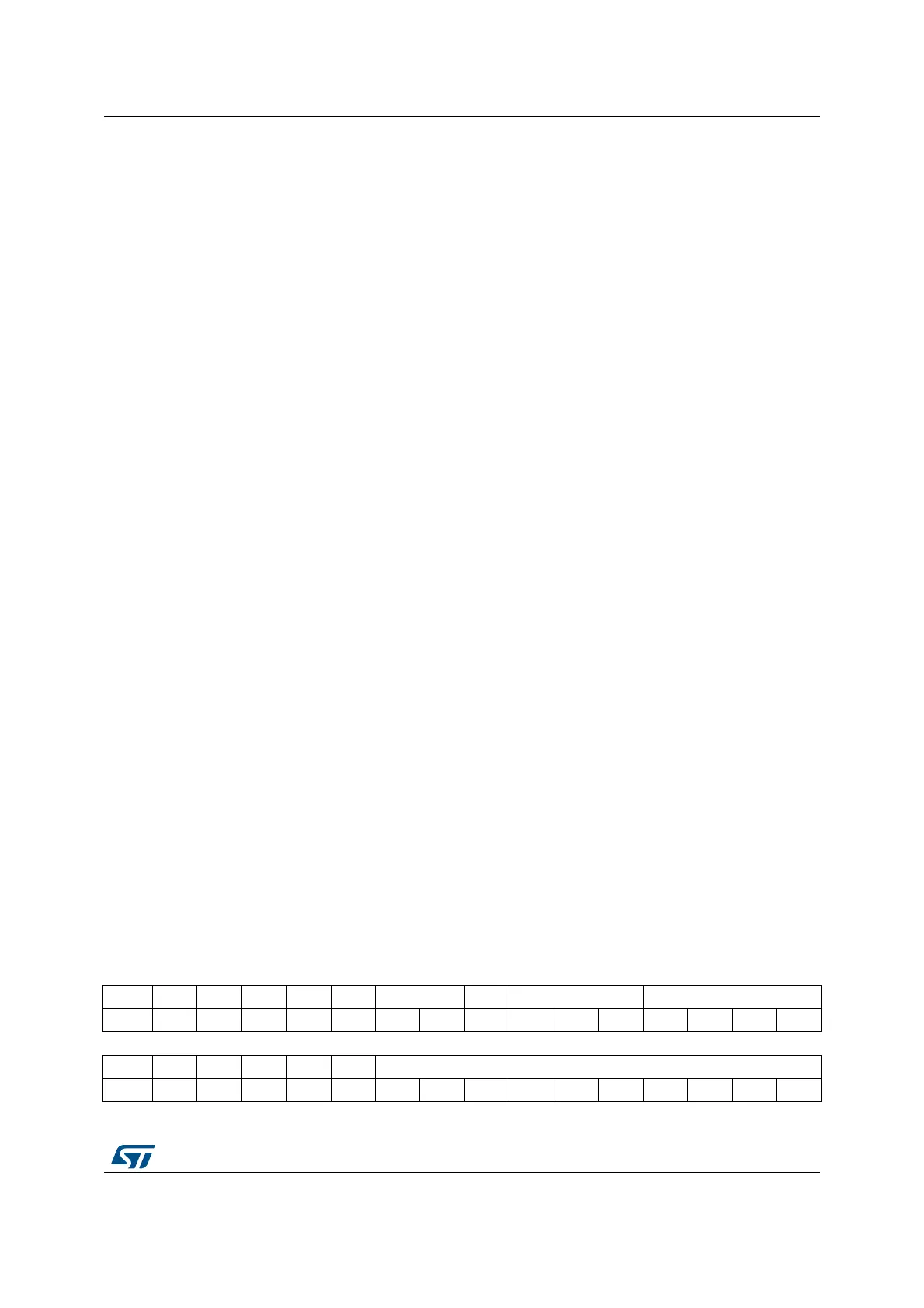

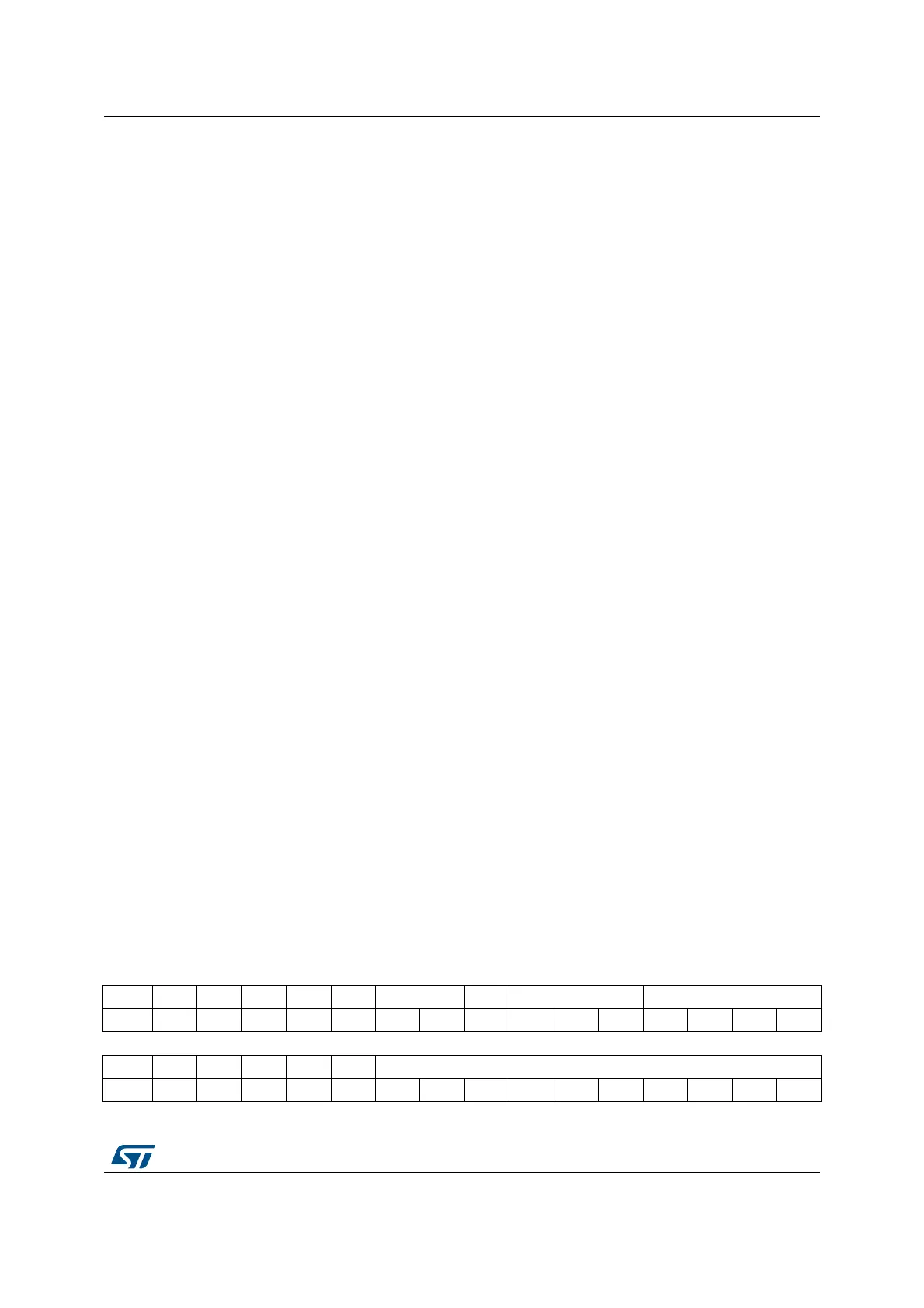

CAN bit timing register (CAN_BTR)

Address offset: 0x1C

Reset value: 0x0123 0000

This register can only be accessed by the software when the CAN hardware is in

initialization mode.

Bits 31:24 REC[7:0]: Receive error counter

The implementing part of the fault confinement mechanism of the CAN protocol. In case of

an error during reception, this counter is incremented by 1 or by 8 depending on the error

condition as defined by the CAN standard. After every successful reception the counter is

decremented by 1 or reset to 120 if its value was higher than 128. When the counter value

exceeds 127, the CAN controller enters the error passive state.

Bits 23:16 TEC[7:0]

: Least significant byte of the 9-bit transmit error counter

The implementing part of the fault confinement mechanism of the CAN protocol.

Bits 15:7 Reserved, must be kept at reset value.

Bits 6:4 LEC[2:0]

: Last error code

This field is set by hardware and holds a code which indicates the error condition of the last

error detected on the CAN bus. If a message has been transferred (reception or

transmission) without error, this field will be cleared to ‘0’.

The LEC[2:0] bits can be set to value 0b111 by software. They are updated by hardware to

indicate the current communication status.

000: No Error

001: Stuff Error

010: Form Error

011: Acknowledgment Error

100: Bit recessive Error

101: Bit dominant Error

110: CRC Error

111: Set by software

Bit 3 Reserved, must be kept at reset value.

Bit 2 BOFF

: Bus-off flag

This bit is set by hardware when it enters the bus-off state. The bus-off state is entered on

TEC overflow, greater than 255, refer to Section 42.7.6 on page 1466.

Bit 1 EPVF: Error passive flag

This bit is set by hardware when the Error Passive limit has been reached (Receive Error

Counter or Transmit Error Counter>127).

Bit 0 EWGF

: Error warning flag

This bit is set by hardware when the warning limit has been reached

(Receive Error Counter or Transmit Error Counter≥96).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

SILM LBKM Res. Res. Res. Res. SJW[1:0] Res. TS2[2:0] TS1[3:0]

rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. Res. Res. BRP[9:0]

rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...