DocID024597 Rev 3 1531/1693

RM0351 USB on-the-go full-speed (OTG_FS)

1644

The application must clear the OTG_GINTSTS register at initialization before unmasking

the interrupt bit to avoid any interrupts generated prior to initialization.

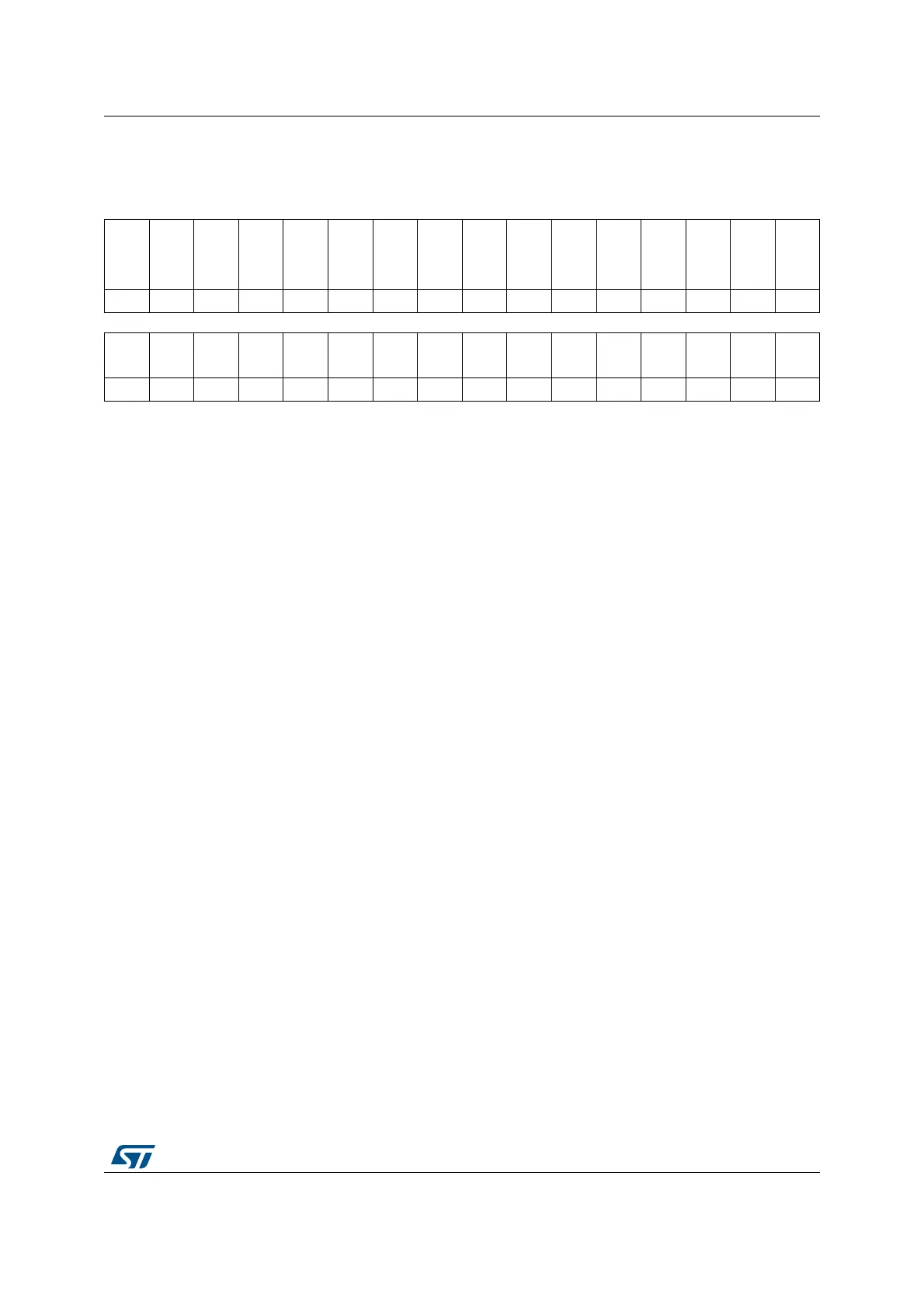

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

WKUP

INT

SRQ

INT

DISC

INT

CIDS

CHG

LPM

INT

PTXFE HCINT

HPRT

INT

RST

DET

Res.

IPXFR/

IN

COMP

ISO

OUT

IISOI

XFR

OEP

INT

IEPINT Res. Res.

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 r r r rc_w1 rc_w1 rc_w1 r r

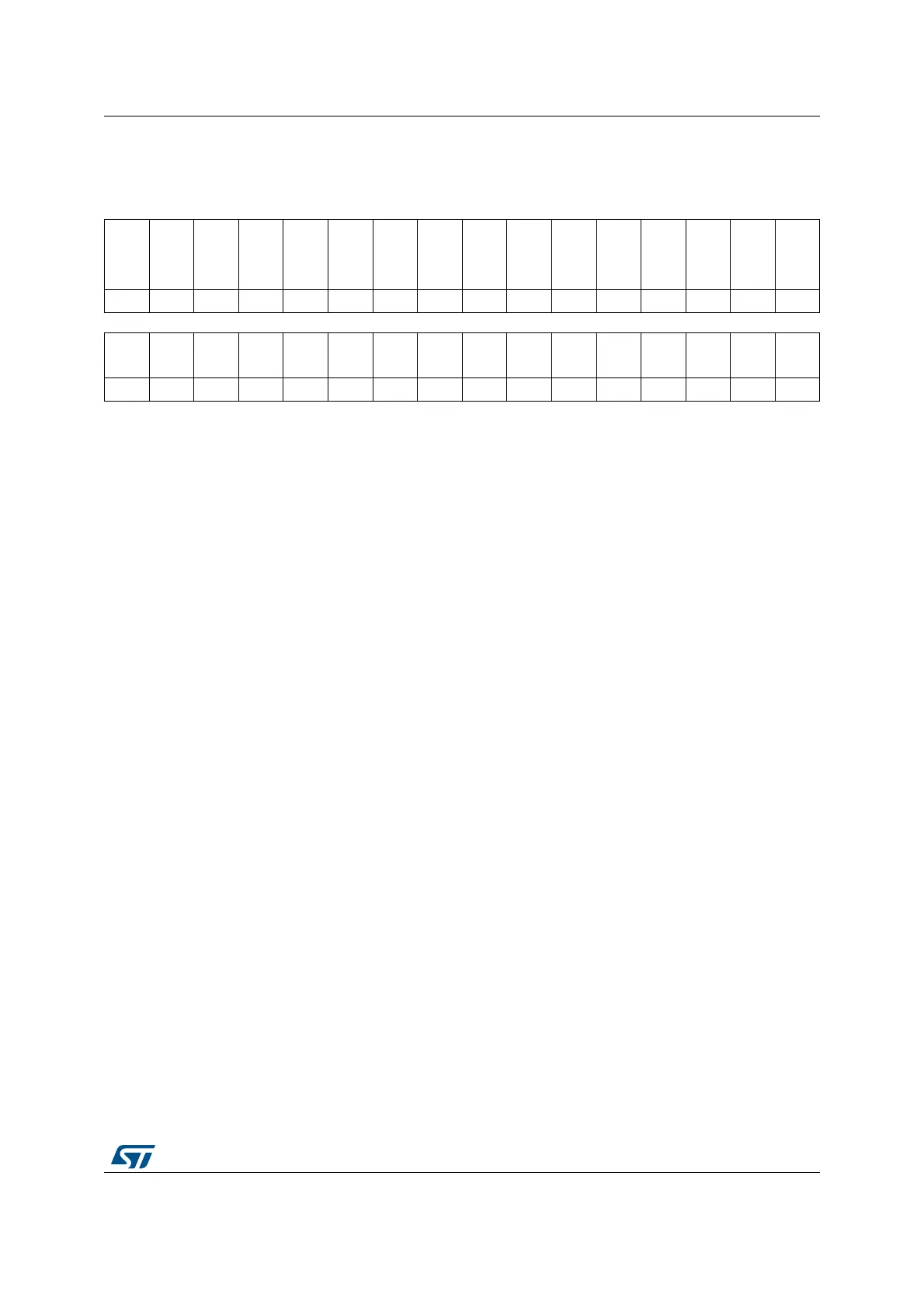

1514131211109876543210

EOPF

ISOO

DRP

ENUM

DNE

USB

RST

USB

SUSP

ESUSP Res. Res.

GO

NAK

EFF

GI

NAK

EFF

NPTXF

E

RXF

LVL

SOF

OTG

INT

MMIS CMOD

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 r r r r rc_w1 r rc_w1 r

Bit 31 WKUPINT: Resume/remote wakeup detected interrupt

Wakeup interrupt during suspend(L2) or LPM(L1) state.

– During suspend(L2):

In device mode, this interrupt is asserted when a resume is detected on the USB. In host

mode, this interrupt is asserted when a remote wakeup is detected on the USB.

– During LPM(L1):

This interrupt is asserted for either Host Initiated Resume or Device Initiated Remote

Wakeup on USB.

Note: Accessible in both device and host modes.

Bit 30 SRQINT: Session request/new session detected interrupt

In host mode, this interrupt is asserted when a session request is detected from the device.

In device mode, this interrupt is asserted when V

BUS

is in the valid range for a B-peripheral

device. Accessible in both device and host modes.

Bit 29 DISCINT: Disconnect detected interrupt

Asserted when a device disconnect is detected.

Note: Only accessible in host mode.

Bit 28 CIDSCHG: Connector ID status change

The core sets this bit when there is a change in connector ID status.

Note: Accessible in both device and host modes.

Bit 27 LPMINT: LPM interrupt

In device mode, this interrupt is asserted when the device receives an LPM transaction and

responds with a non-ERRORed response.

In host mode, this interrupt is asserted when the device responds to an LPM transaction with

a non-ERRORed response or when the host core has completed LPM transactions for the

programmed number of times (RETRYCNT bit in OTG_GLPMCFG).

This field is valid only if the LPMCAP bit in OTG_GLPMCFG is set to 1.

Bit 26 PTXFE: Periodic Tx FIFO empty

Asserted when the periodic transmit FIFO is either half or completely empty and there is

space for at least one entry to be written in the periodic request queue. The half or

completely empty status is determined by the periodic Tx FIFO empty level bit in the

OTG_GAHBCFG register (PTXFELVL bit in OTG_GAHBCFG).

Note: Only accessible in host mode.

Loading...

Loading...