DocID024597 Rev 3 1577/1693

RM0351 USB on-the-go full-speed (OTG_FS)

1644

43.15.45 OTG device endpoint-x control register (OTG_DOEPCTLx)

(x = 1..5 , where x = Endpoint_number)

Address offset for OUT endpoints: 0xB00 + (Endpoint_number × 0x20)

Reset value: 0x0000 0000

The application uses this register to control the behavior of each logical endpoint other than

endpoint 0.

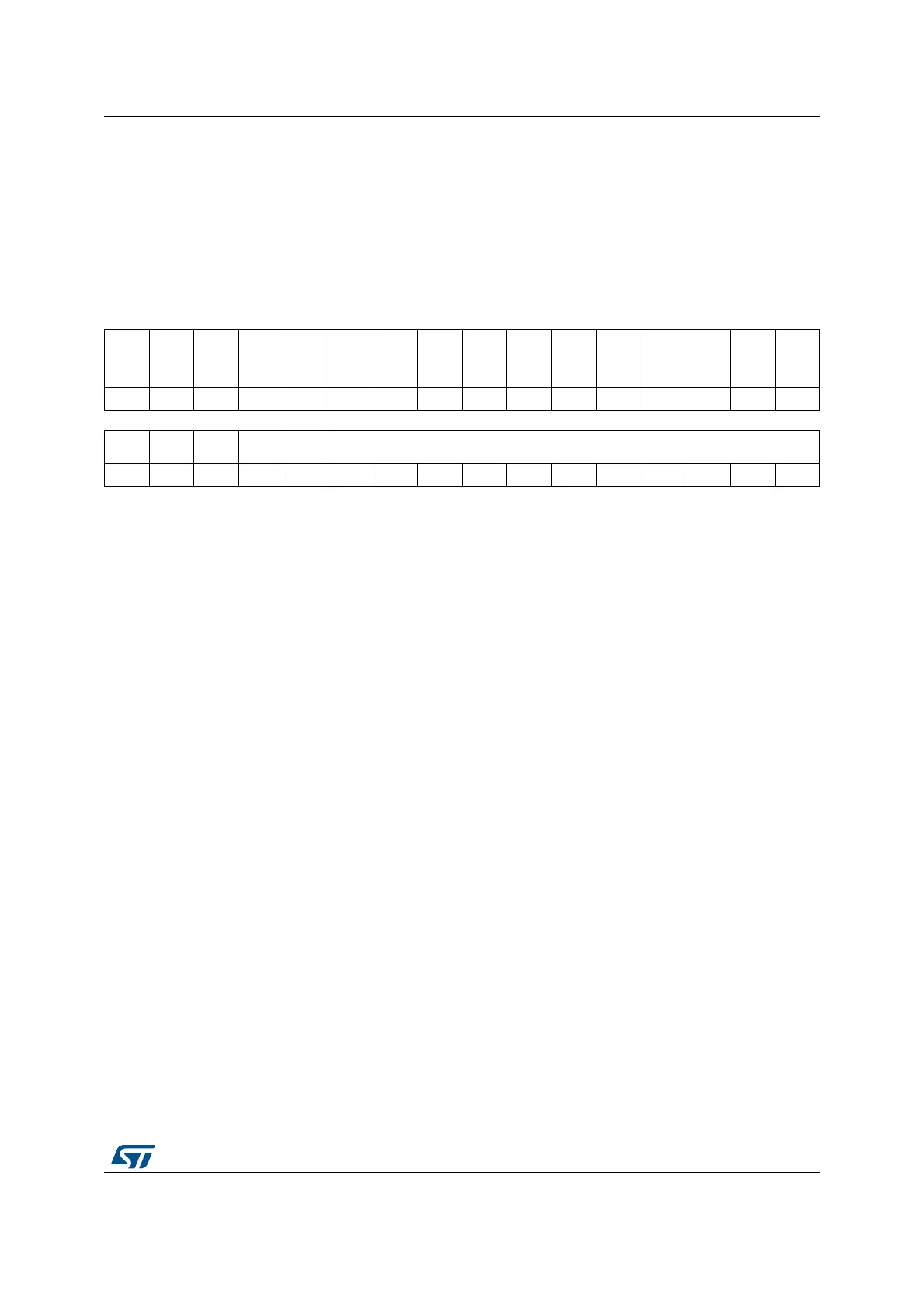

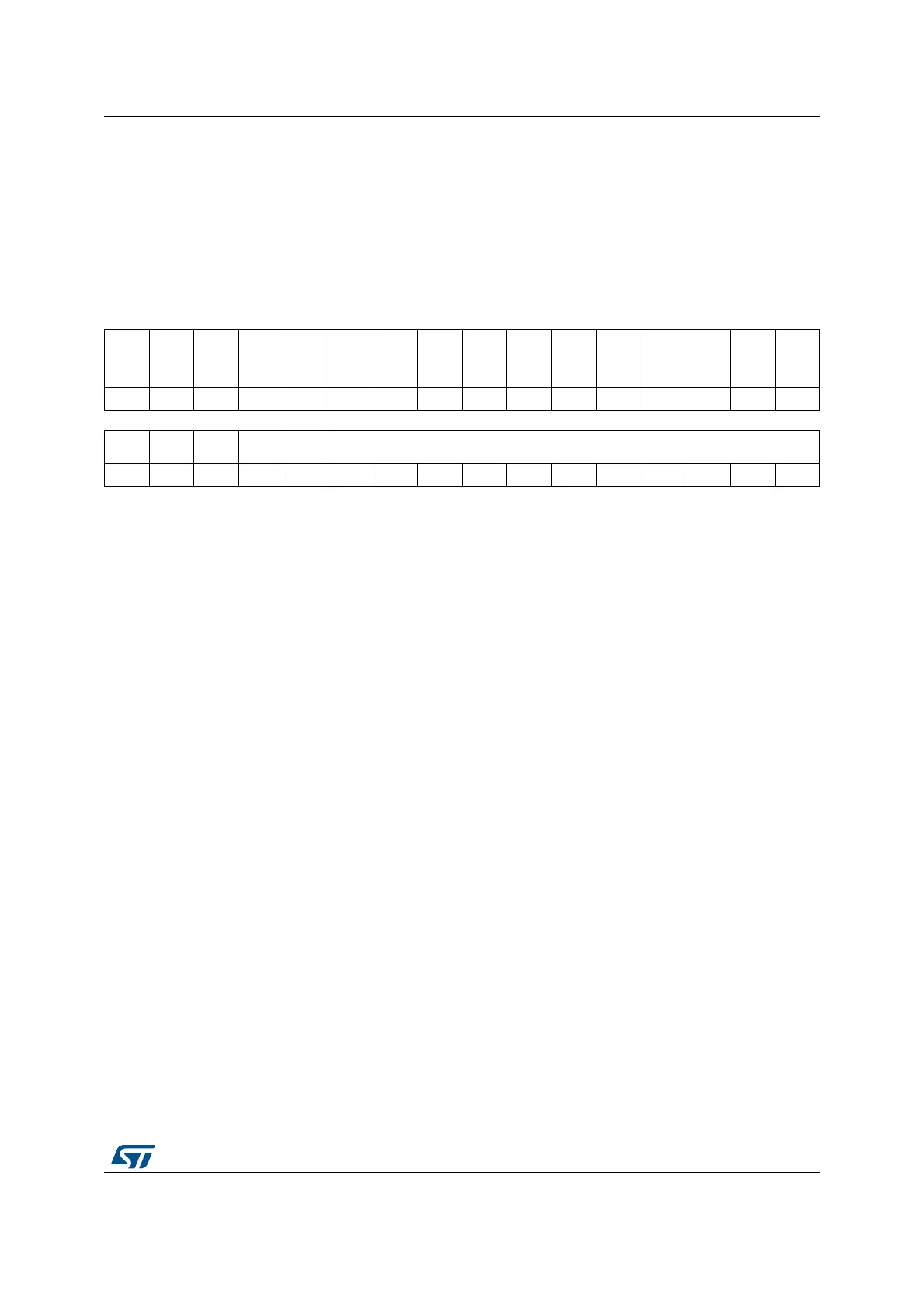

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EPENA EPDIS

SD1

PID/

SODD

FRM

SD0

PID/

SEVN

FRM

SNAK CNAK Res. Res. Res. Res. STALL SNPM EPTYP

NAK

STS

EO

NUM/

DPID

rs rs w w w w rw/rs rw rw rw r r

1514131211109876543210

USBA

EP

Res. Res. Res. Res. MPSIZ

rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 EPENA: Endpoint enable

Applies to IN and OUT endpoints.

The application sets this bit to start transmitting data on an endpoint.

The core clears this bit before setting any of the following interrupts on this endpoint:

– SETUP phase done

– Endpoint disabled

– Transfer completed

Bit 30 EPDIS: Endpoint disable

The application sets this bit to stop transmitting/receiving data on an endpoint, even before

the transfer for that endpoint is complete. The application must wait for the Endpoint

disabled interrupt before treating the endpoint as disabled. The core clears this bit before

setting the Endpoint disabled interrupt. The application must set this bit only if Endpoint

enable is already set for this endpoint.

Bit 29 SD1PID: Set DATA1 PID

Applies to interrupt/bulk IN and OUT endpoints only. Writing to this field sets the endpoint

data PID (DPID) field in this register to DATA1.

SODDFRM: Set odd frame

Applies to isochronous IN and OUT endpoints only. Writing to this field sets the Even/Odd

frame (EONUM) field to odd frame.

Bit 28 SD0PID: Set DATA0 PID

Applies to interrupt/bulk OUT endpoints only.

Writing to this field sets the endpoint data PID (DPID) field in this register to DATA0.

SEVNFRM: Set even frame

Applies to isochronous OUT endpoints only.

Writing to this field sets the Even/Odd frame (EONUM) field to even frame.

Bit 27 SNAK: Set NAK

A write to this bit sets the NAK bit for the endpoint.

Using this bit, the application can control the transmission of NAK handshakes on an

endpoint. The core can also set this bit for OUT endpoints on a Transfer Completed

interrupt, or after a SETUP is received on the endpoint.

Loading...

Loading...