Direct memory access controller (DMA) RM0351

300/1693 DocID024597 Rev 3

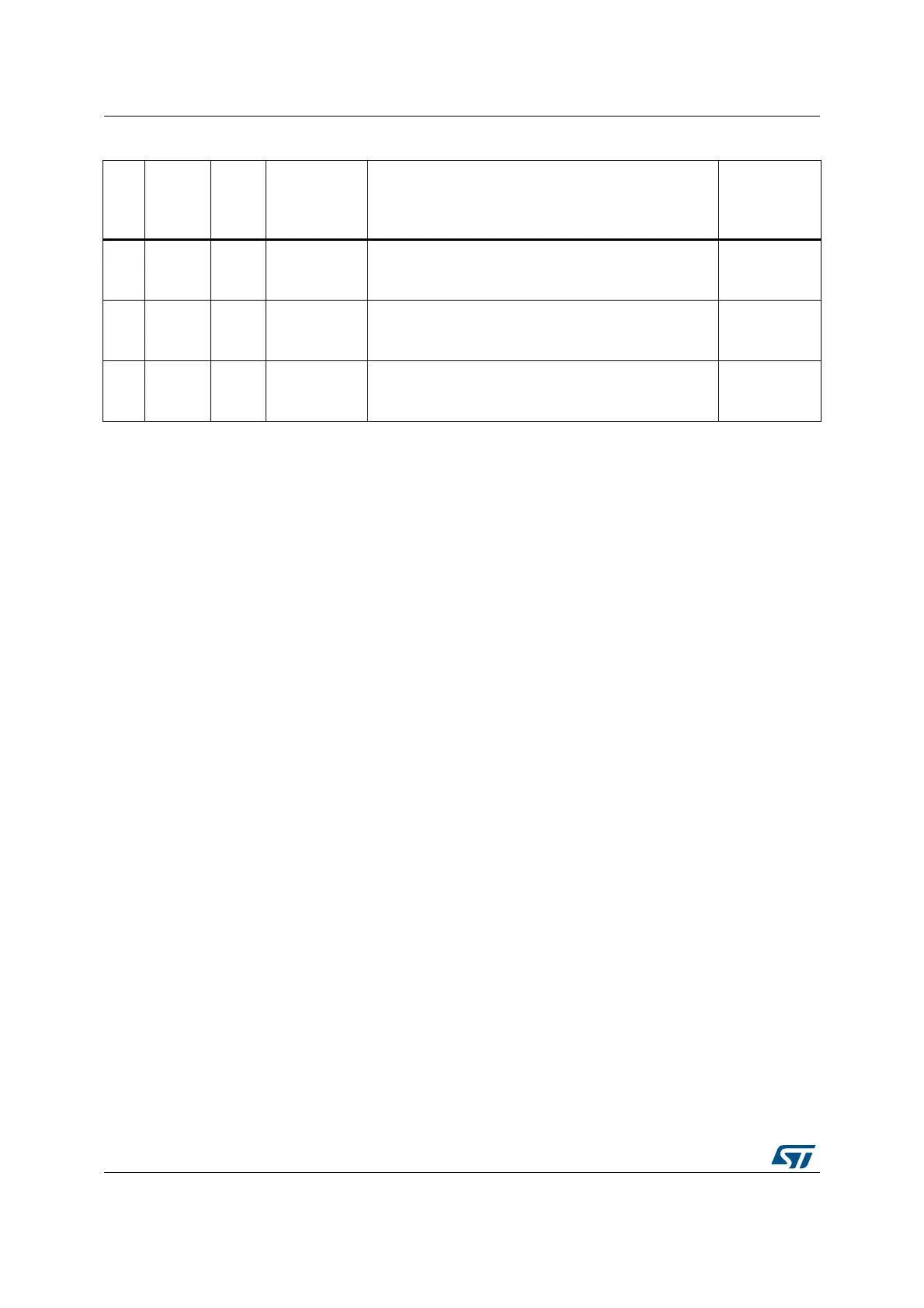

32 8 4

@0x0 / B3B2B1B0

@0x4 / B7B6B5B4

@0x8 / BBBAB9B8

@0xC / BFBEBDBC

1: READ B3B2B1B0[31:0] @0x0 then WRITE B0[7:0] @0x0

2: READ B7B6B5B4[31:0] @0x4 then WRITE B4[7:0] @0x1

3: READ BBBAB9B8[31:0] @0x8 then WRITE B8[7:0] @0x2

4: READ BFBEBDBC[31:0] @0xC then WRITE BC[7:0] @0x3

@0x0 / B0

@0x1 / B4

@0x2 / B8

@0x3 / BC

32 16 4

@0x0 / B3B2B1B0

@0x4 / B7B6B5B4

@0x8 / BBBAB9B8

@0xC / BFBEBDBC

1: READ B3B2B1B0[31:0] @0x0 then WRITE B1B0[15:0] @0x0

2: READ B7B6B5B4[31:0] @0x4 then WRITE B5B4[15:0] @0x2

3: READ BBBAB9B8[31:0] @0x8 then WRITE B9B8[15:0] @0x4

4: READ BFBEBDBC[31:0] @0xC then WRITE BDBC[15:0] @0x6

@0x0 / B1B0

@0x2 / B5B4

@0x4 / B9B8

@0x6 / BDBC

32 32 4

@0x0 / B3B2B1B0

@0x4 / B7B6B5B4

@0x8 / BBBAB9B8

@0xC / BFBEBDBC

1: READ B3B2B1B0[31:0] @0x0 then WRITE B3B2B1B0[31:0] @0x0

2: READ B7B6B5B4[31:0] @0x4 then WRITE B7B6B5B4[31:0] @0x4

3: READ BBBAB9B8[31:0] @0x8 then WRITE BBBAB9B8[31:0] @0x8

4: READ BFBEBDBC[31:0] @0xC then WRITE BFBEBDBC[31:0] @0xC

@0x0 / B3B2B1B0

@0x4 / B7B6B5B4

@0x8 / BBBAB9B8

@0xC / BFBEBDBC

Table 37. Programmable data width & endian behavior (when bits PINC = MINC = 1) (continued)

Source

port

width

Destination

port width

Number

of data

items to

transfer

(NDT)

Source content:

address / data

Transfer operations

Destination

content:

address / data

Loading...

Loading...