Nested vectored interrupt controller (NVIC) RM0351

322/1693 DocID024597 Rev 3

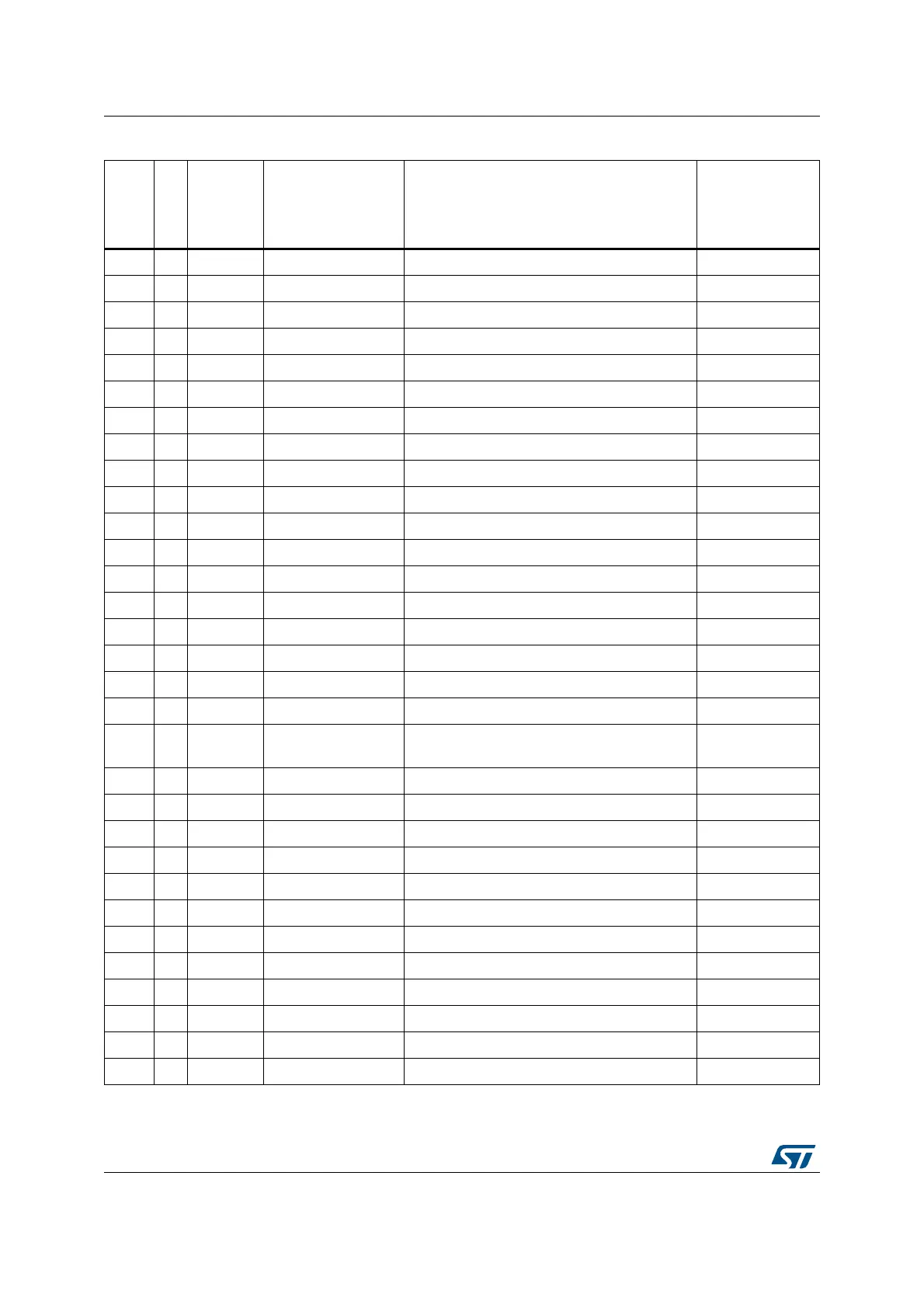

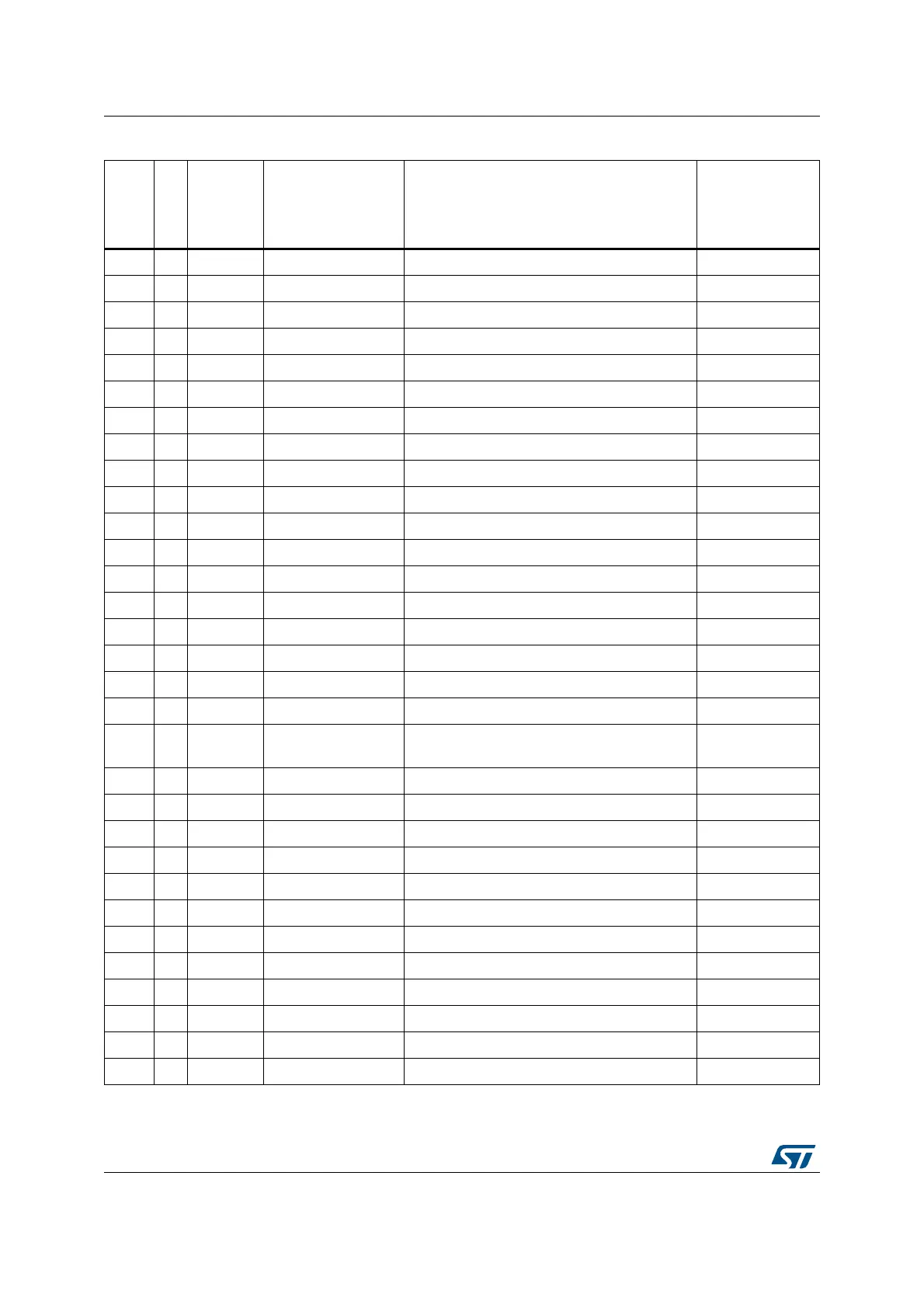

46 53 settable TIM1_CC TIM8 capture compare interrupt 0x0000 00F8

47 54 settable ADC3 ADC3 global interrupt 0x0000 00FC

48 55 settable FMC FMC global interrupt 0x0000 0100

49 56 settable SDMMC1 SDMMC1 global interrupt 0x0000 0104

50 57 settable TIM5 TIM5 global interrupt 0x0000 0108

51 58 settable SPI3 SPI3 global interrupt 0x0000 010C

52 59 settable UART4 UART4 global interrupt 0x0000 0110

53 60 settable UART5 UART5 global interrupt 0x0000 0114

54 61 settable TIM6_DACUNDER TIM6 global and DAC12 underrun interrupts 0x0000 0118

55 62 settable TIM7 TIM7 global interrupt 0x0000 011C

56 63 settable DMA2_CH1 DMA2 channel 1 interrupt 0x0000 0120

57 64 settable DMA2_CH2 DMA2 channel 2 interrupt 0x0000 0124

58 65 settable DMA2_CH3 DMA2 channel 3 interrupt 0x0000 0128

59 66 settable DMA2_CH4 DMA2 channel 4 interrupt 0x0000 012C

60 67 settable DMA2_CH5 DMA2 channel 5 interrupt 0x0000 0130

61 68 settable DFSDM0 DFSDM0 global interrupt 0x0000 0134

62 69 settable DFSDM1 DFSDM1 global interrupt 0x0000 0138

63 70 settable DFSDM2 DFSDM2 global interrupt 0x0000 013C

64 71 settable COMP

COMP1/COMP2 through EXTI lines 21/22

interrupts

0x0000 0140

65 72 settable LPTIM1 LPTIM1 global interrupt 0x0000 0144

66 73 settable LPTIM2 LPTIM2 global interrupt 0x0000 0148

67 74 settable OTG_FS OTG_FS global interrupt 0x0000 014C

68 75 settable DMA2_CH6 DMA2 channel 6 interrupt 0x0000 0150

69 76 settable DMA2_CH7 DMA2 channel 7 interrupt 0x0000 0154

70 77 settable LPUART1 LPUART1 global interrupt 0x0000 0158

71 78 settable QUADSPI QUADSPI global interrupt 0x0000 015C

72 79 settable I2C3_EV I2C3 event interrupt 0x0000 0160

73 79 settable I2C3_ER I2C3 error interrupt 0x0000 0164

74 80 settable SAI1 SAI1 global interrupt 0x0000 0168

75 74 settable SAI2 SAI2 global interrupt 0x0000 016C

76 75 settable SWPMI1 SWPMI1 global interrupt 0x0000 0170

Table 42. STM32L4x6 vector table (continued)

Position

Priority

Type of

priority

Acronym Description Address

Loading...

Loading...