DocID024597 Rev 3 573/1693

RM0351 Digital-to-analog converter (DAC)

573

Refer to Section 2.2.2: Memory map and register boundary addresses for the register

boundary addresses.

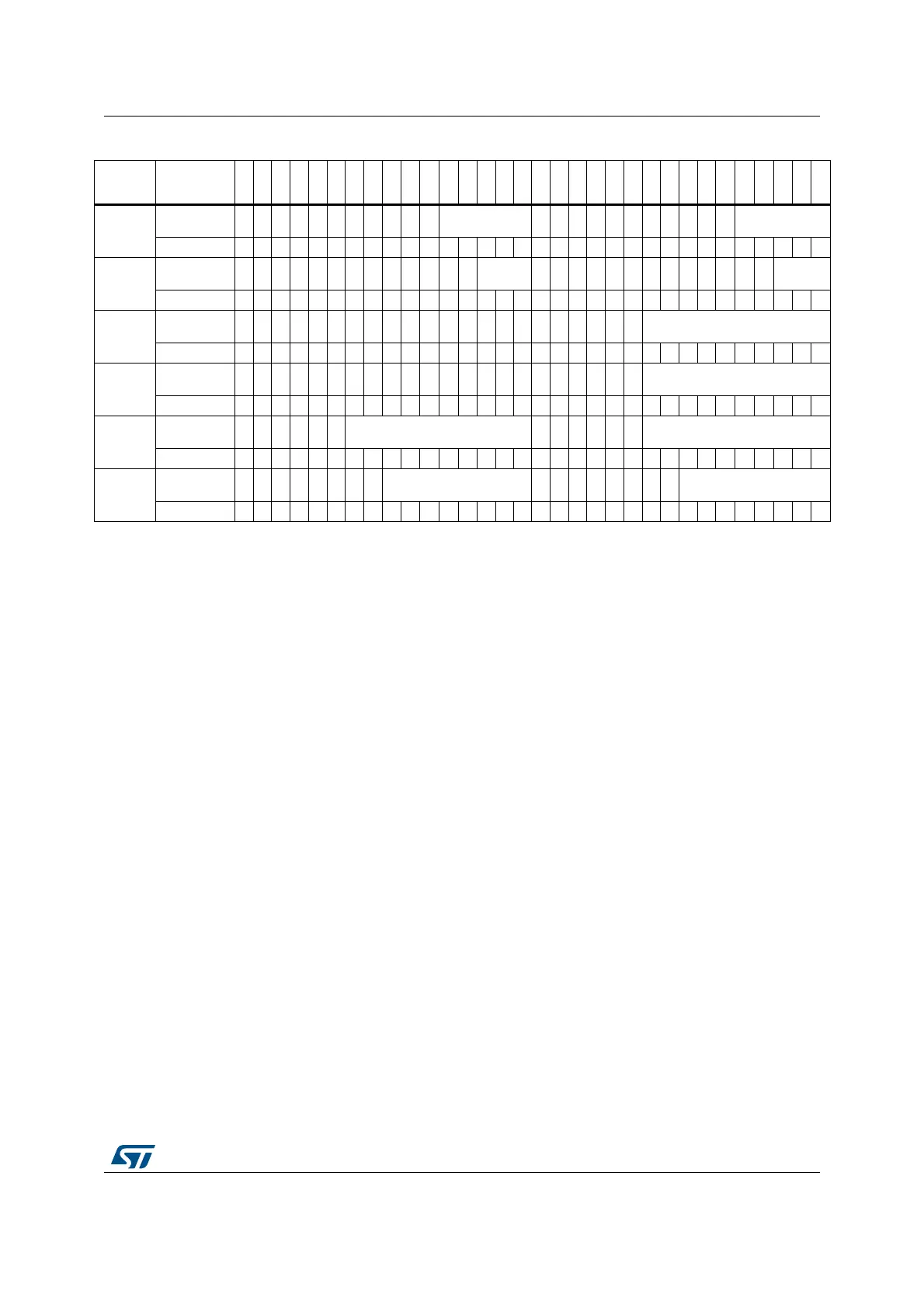

0x38

DAC_CCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

OTRIM2[4:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

OTRIM1[4:0]

Reset value

XXXXX XXXXX

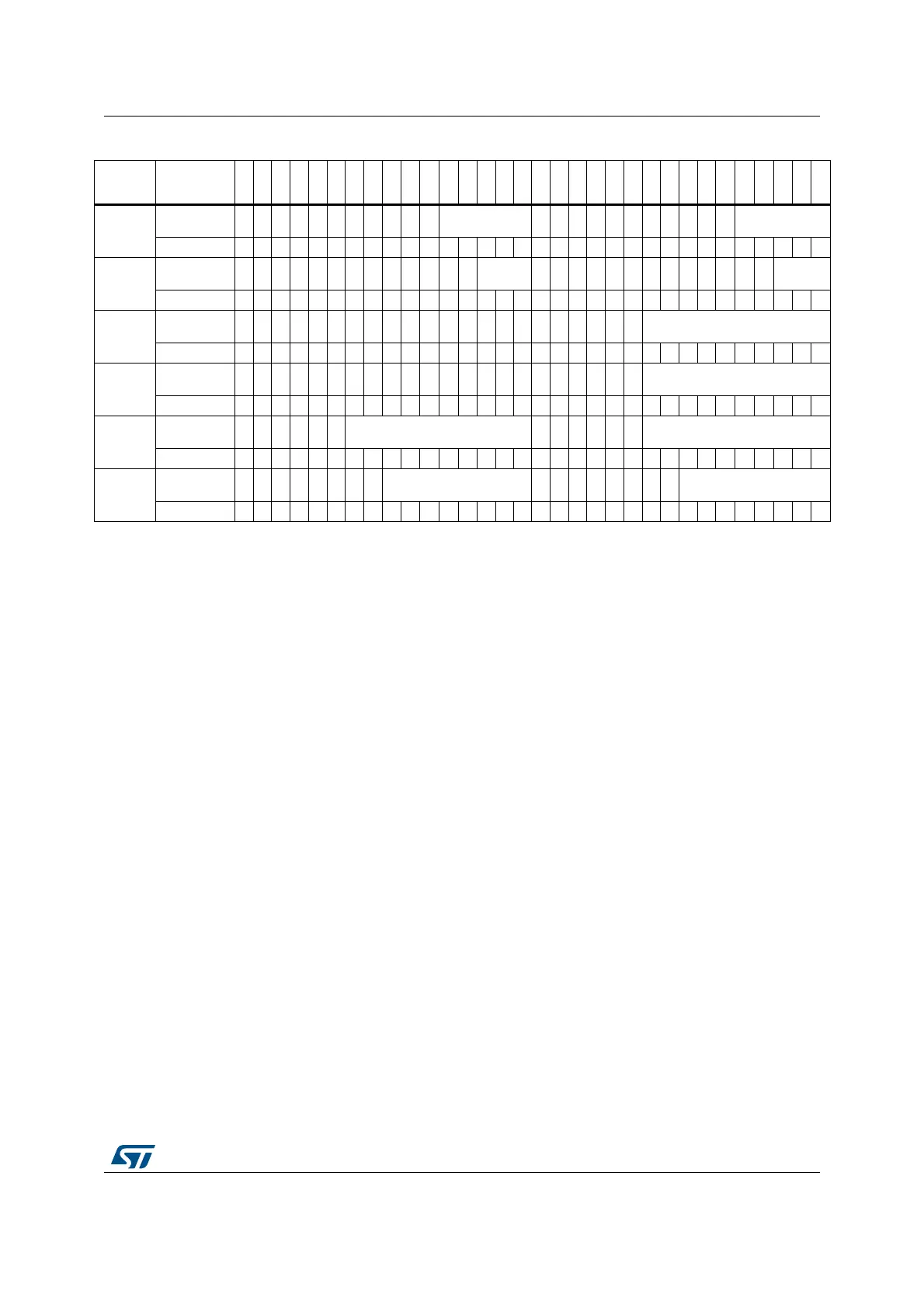

0x3C

DAC_MCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

MODE2

[2:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

MODE1

[2:0]

Reset value 0 0 0 0 0 0

0x40

DAC_SHSR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

TSAMPLE1[9:0]

Reset value 0000000000

0x44

DAC_SHSR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

TSAMPLE2[9:0]

Reset value 0000000000

0x48

DAC_SHHR

Res.

Res.

Res.

Res.

Res.

Res.

THOLD2[9:0]

Res.

Res.

Res.

Res.

Res.

Res.

THOLD1[9:0]

Reset value 0000000001 0000000001

0x4C

DAC_SHRR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

TREFRESH2[7:0]

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

TREFRESH1[7:0]

Reset value 00000001 00000001

Table 106. DAC register map

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...