DocID024597 Rev 3 633/1693

RM0351 Digital filter for sigma delta modulators (DFSDM)

657

21.6.4 DFSDM channel watchdog filter data register (DFSDM_CHWDATyR)

(y=0..7)

This register contains the data resulting from the analog watchdog filter associated to the

input channels.

Address offset: 0x0C

Reset value: 0x0000 0000

21.6.5 DFSDM channel data input register (DFSDM_CHDATINyR)

(y=0..7)

This register contains 16-bit input data to be processed by DFSDM filter module.

Address offset: 0x10

Reset value: 0x0000 0000

Bits 15:12 BKSCD[3:0]: Break signal assignment for short-circuit detector on channel y

BKSCD[i] = 0: Break i signal not assigned to short-circuit detector on channel y

BKSCD[i] = 1: Break i signal assigned to short-circuit detector on channel y

Bits 11:8 Reserved, must be kept at reset value.

Bits 7:0 SCDT[7:0]: short-circuit detector threshold for channel y

These bits are written by software to define the threshold counter for the short-circuit detector. If this

value is reached, then a short-circuit detector event occurs on a given channel.

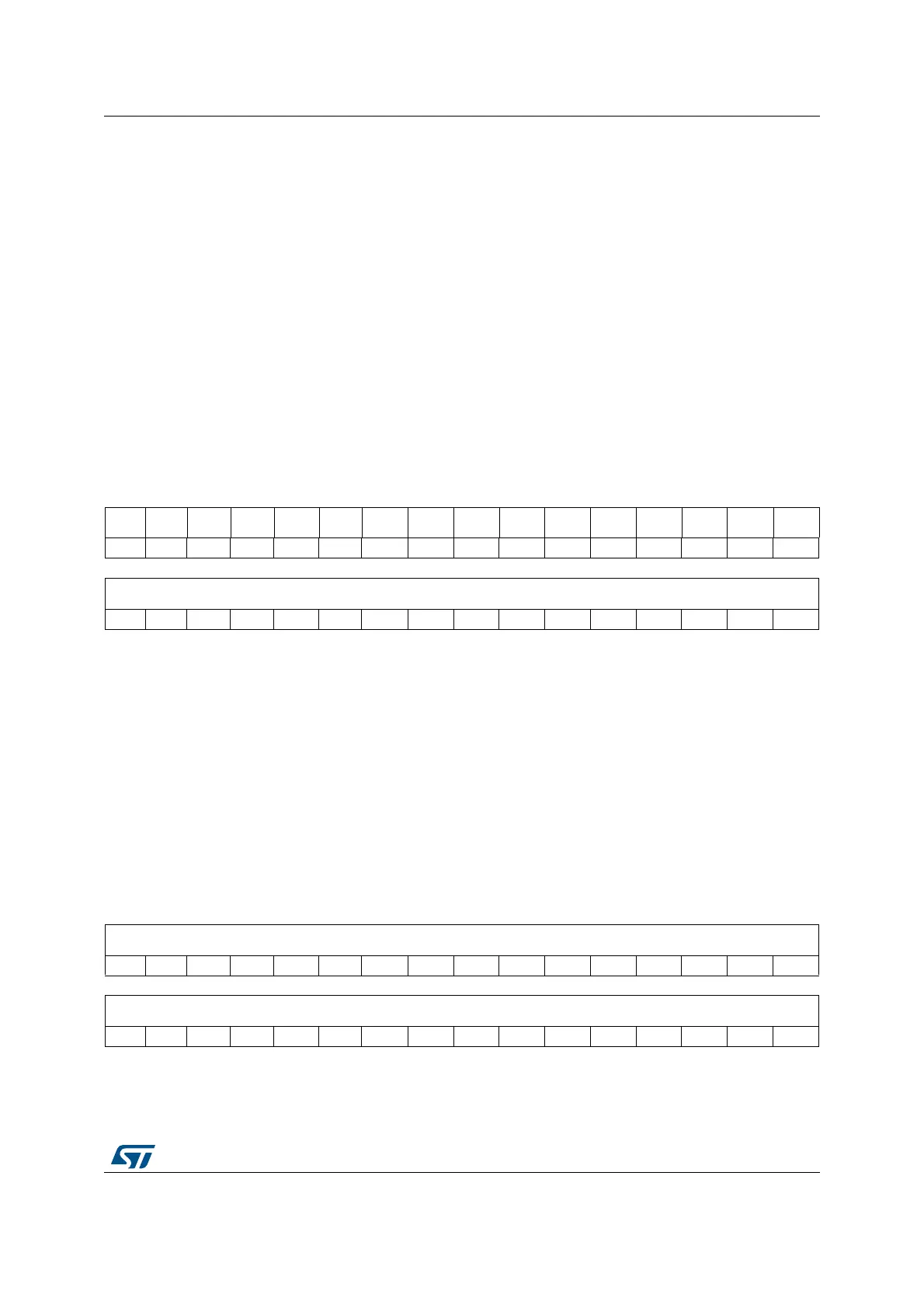

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

WDATA[15:0]

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 WDATA[15:0]: Input channel y watchdog data

Data converted by the analog watchdog filter for input channel y. This data is continuously converted

(no trigger) for this channel, with a limited resolution (OSR=1...32/sinc order = 1...3).

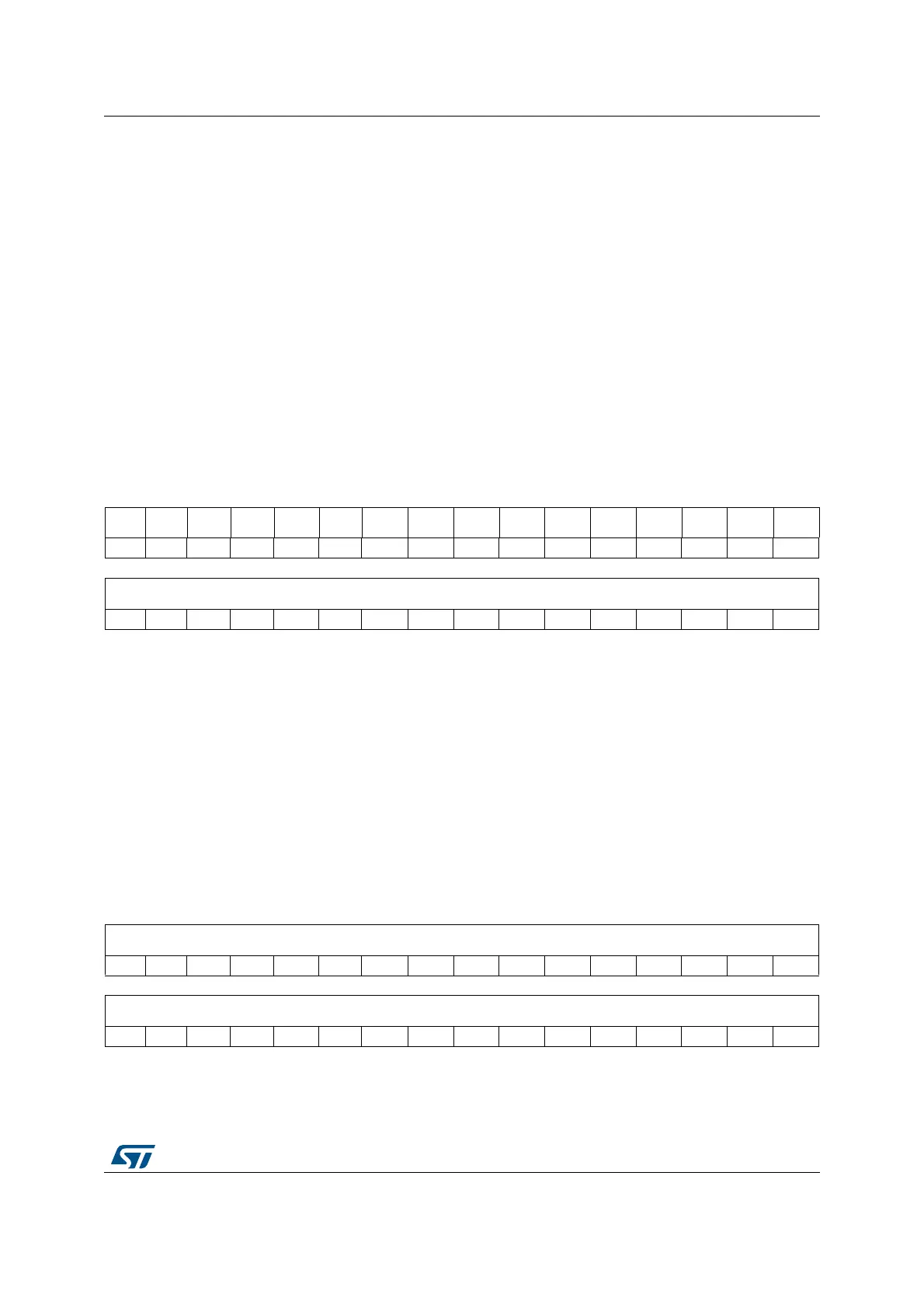

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

INDAT1[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

INDAT0[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...