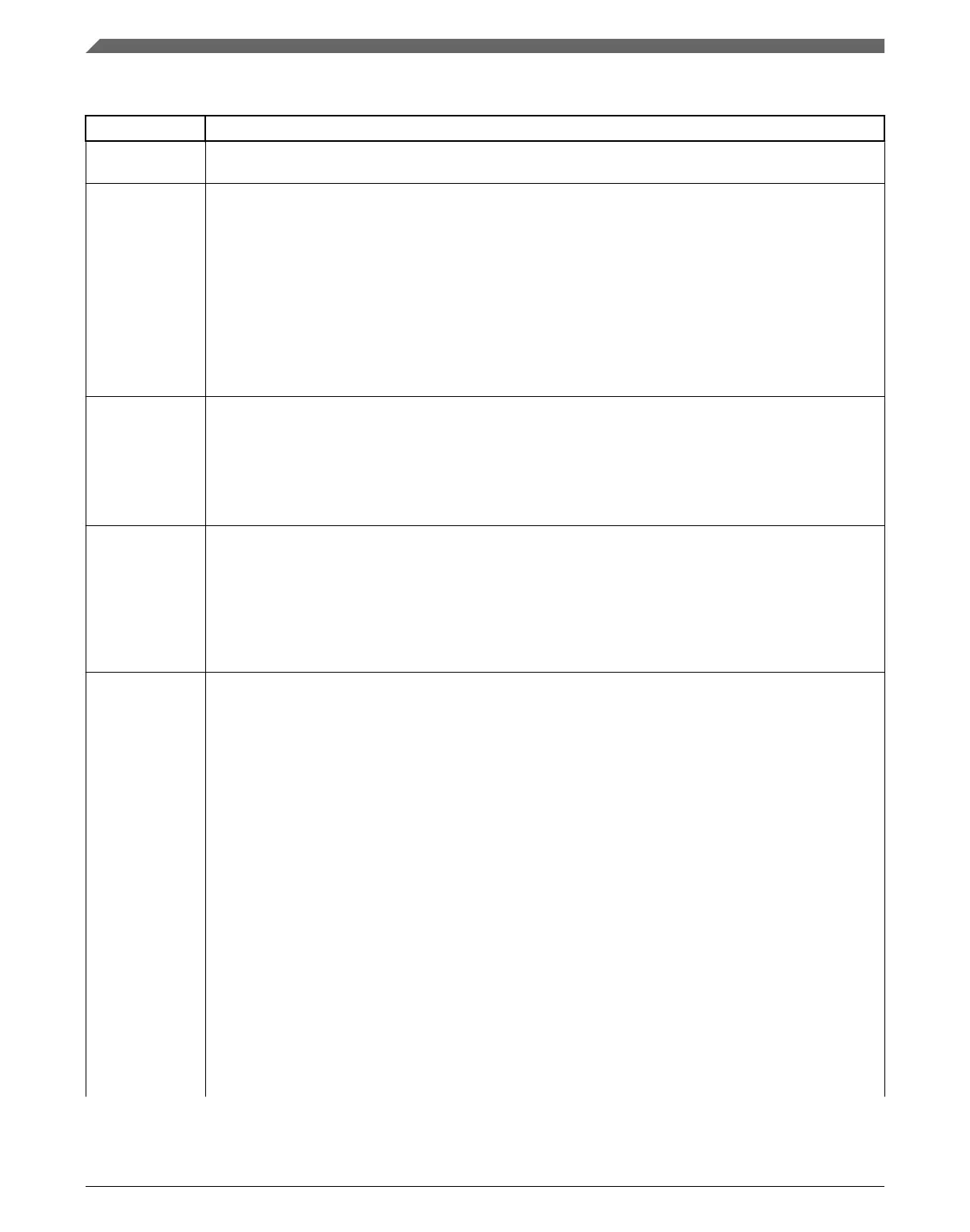

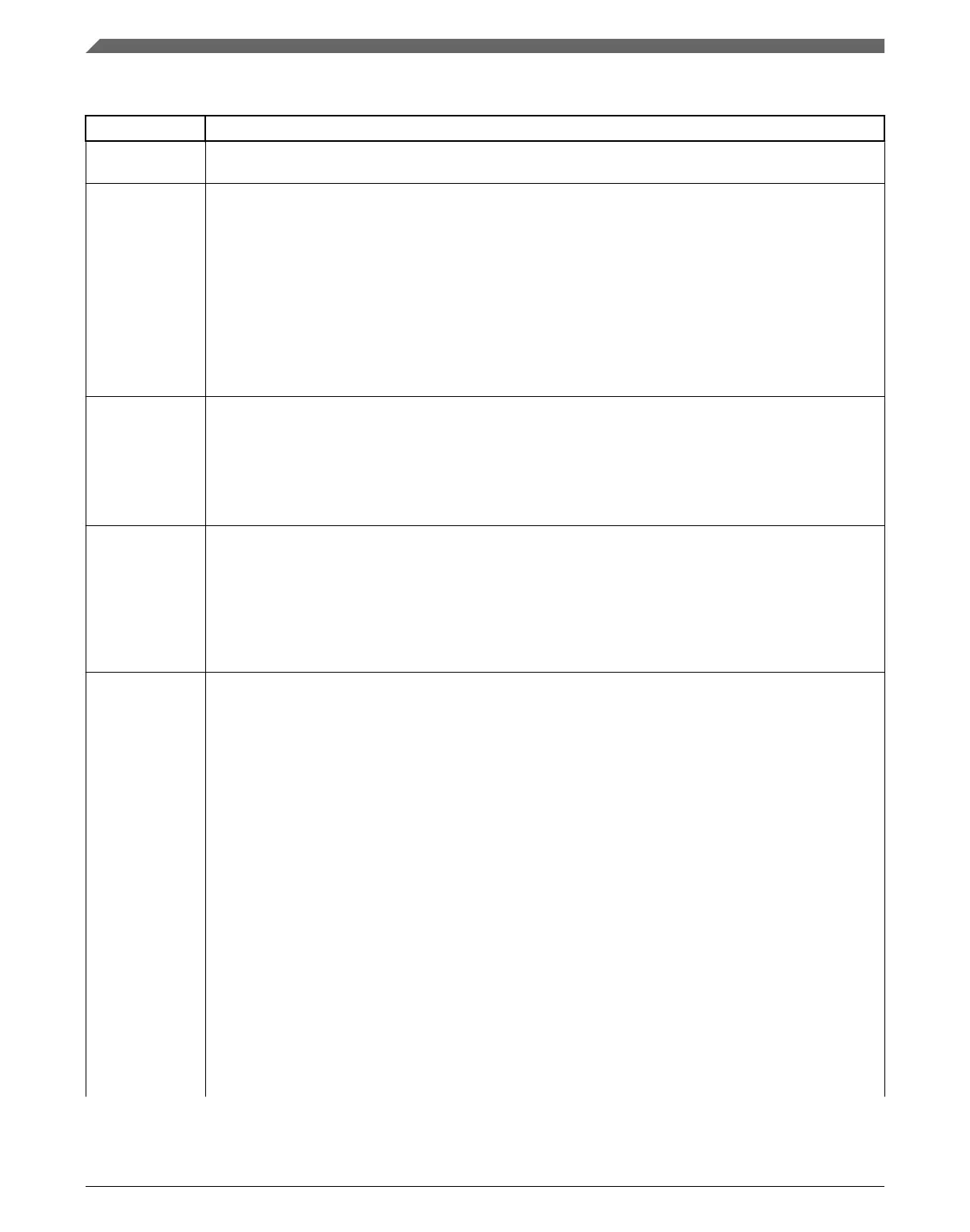

ADCx_SC1n field descriptions

Field Description

31–8

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

7

COCO

Conversion Complete Flag

This is a read-only field that is set each time a conversion is completed when the compare function is

disabled, or SC2[ACFE]=0 and the hardware average function is disabled, or SC3[AVGE]=0. When the

compare function is enabled, or SC2[ACFE]=1, COCO is set upon completion of a conversion only if the

compare result is true. When the hardware average function is enabled, or SC3[AVGE]=1, COCO is set

upon completion of the selected number of conversions (determined by AVGS). COCO in SC1A is also set

at the completion of a calibration sequence. COCO is cleared when the respective SC1n register is written

or when the respective Rn register is read.

0 Conversion is not completed.

1 Conversion is completed.

6

AIEN

Interrupt Enable

Enables conversion complete interrupts. When COCO becomes set while the respective AIEN is high, an

interrupt is asserted.

0 Conversion complete interrupt is disabled.

1 Conversion complete interrupt is enabled.

5

DIFF

Differential Mode Enable

Configures the ADC to operate in differential mode. When enabled, this mode automatically selects from

the differential channels, and changes the conversion algorithm and the number of cycles to complete a

conversion.

0 Single-ended conversions and input channels are selected.

1 Differential conversions and input channels are selected.

ADCH Input channel select

Selects one of the input channels. The input channel decode depends on the value of DIFF. DAD0-DAD3

are associated with the input pin pairs DADPx and DADMx.

NOTE:

Some of the input channel options in the bitfield-setting descriptions might not be available for

your device. For the actual ADC channel assignments for your device, see the Chip Configuration

details.

The successive approximation converter subsystem is turned off when the channel select bits are all set,

that is, ADCH = 11111. This feature allows explicit disabling of the ADC and isolation of the input channel

from all sources. Terminating continuous conversions this way prevents an additional single conversion

from being performed. It is not necessary to set ADCH to all 1s to place the ADC in a low-power state

when continuous conversions are not enabled because the module automatically enters a low-power state

when a conversion completes.

00000

When DIFF=0, DADP0 is selected as input; when DIFF=1, DAD0 is selected as input.

00001 When DIFF=0, DADP1 is selected as input; when DIFF=1, DAD1 is selected as input.

00010 When DIFF=0, DADP2 is selected as input; when DIFF=1, DAD2 is selected as input.

00011 When DIFF=0, DADP3 is selected as input; when DIFF=1, DAD3 is selected as input.

00100 When DIFF=0, AD4 is selected as input; when DIFF=1, it is reserved.

00101 When DIFF=0, AD5 is selected as input; when DIFF=1, it is reserved.

00110 When DIFF=0, AD6 is selected as input; when DIFF=1, it is reserved.

00111 When DIFF=0, AD7 is selected as input; when DIFF=1, it is reserved.

Table continues on the next page...

Memory map and register definitions

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

770 NXP Semiconductors

Loading...

Loading...