If (SYNCMODE = 0), (SYNCHOM = 1), and (PWMSYNC = 0), then this

synchronization is done on the next enabled trigger event. If the trigger event was a

software trigger, then the SWSYNC bit is cleared on the next selected loading point. If

the trigger event was a hardware trigger, then the TRIGn bit is cleared according to

Hardware trigger. Examples with software and hardware triggers follow.

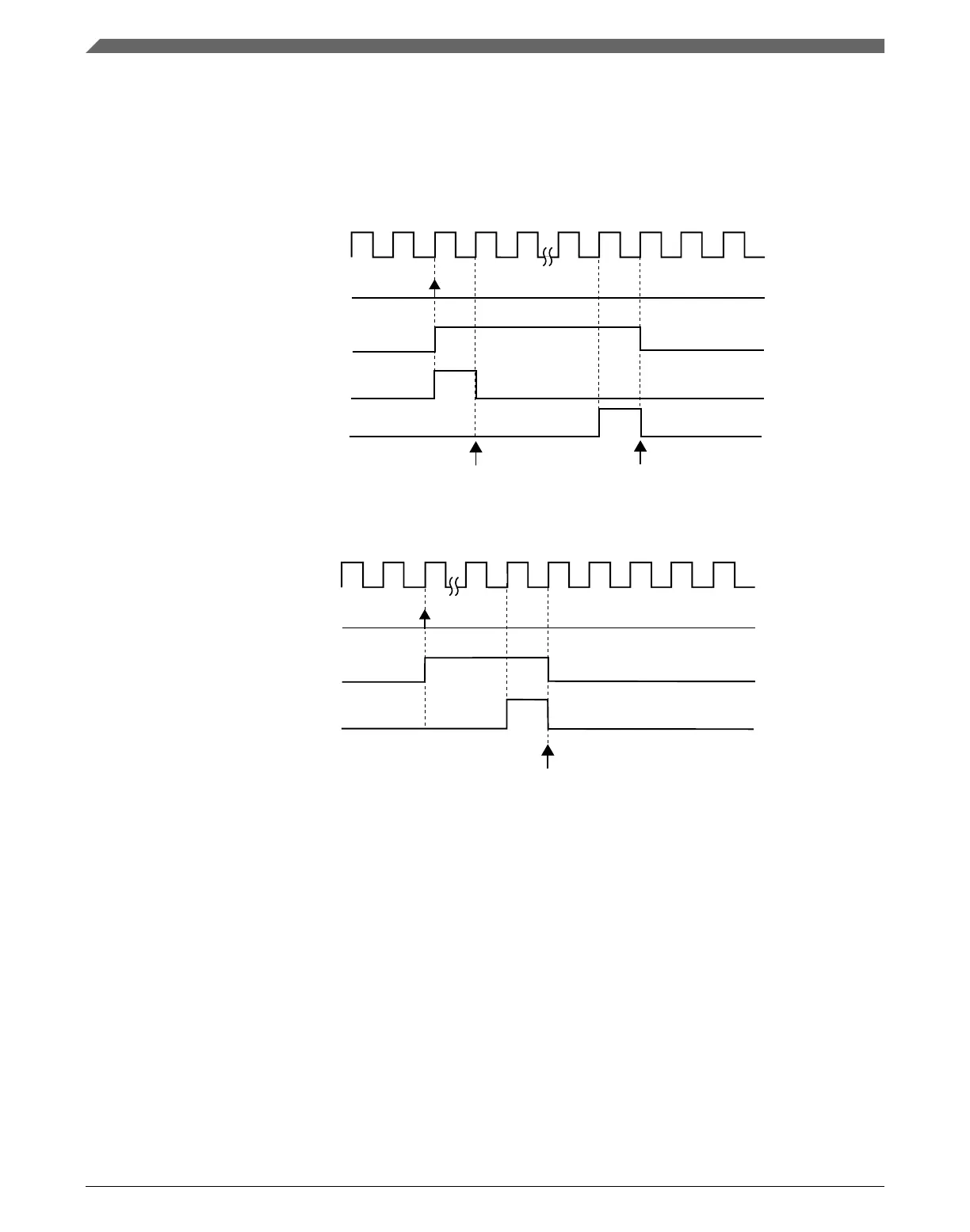

system clock

OUTMASK register is updated

selected loading point

SWSYNC bit is cleared

write 1 to SWSYNC bit

SWSYNC bit

software trigger event

Figure 39-53. OUTMASK synchronization with (SYNCMODE = 0), (SYNCHOM = 1),

(PWMSYNC = 0) and software trigger was used

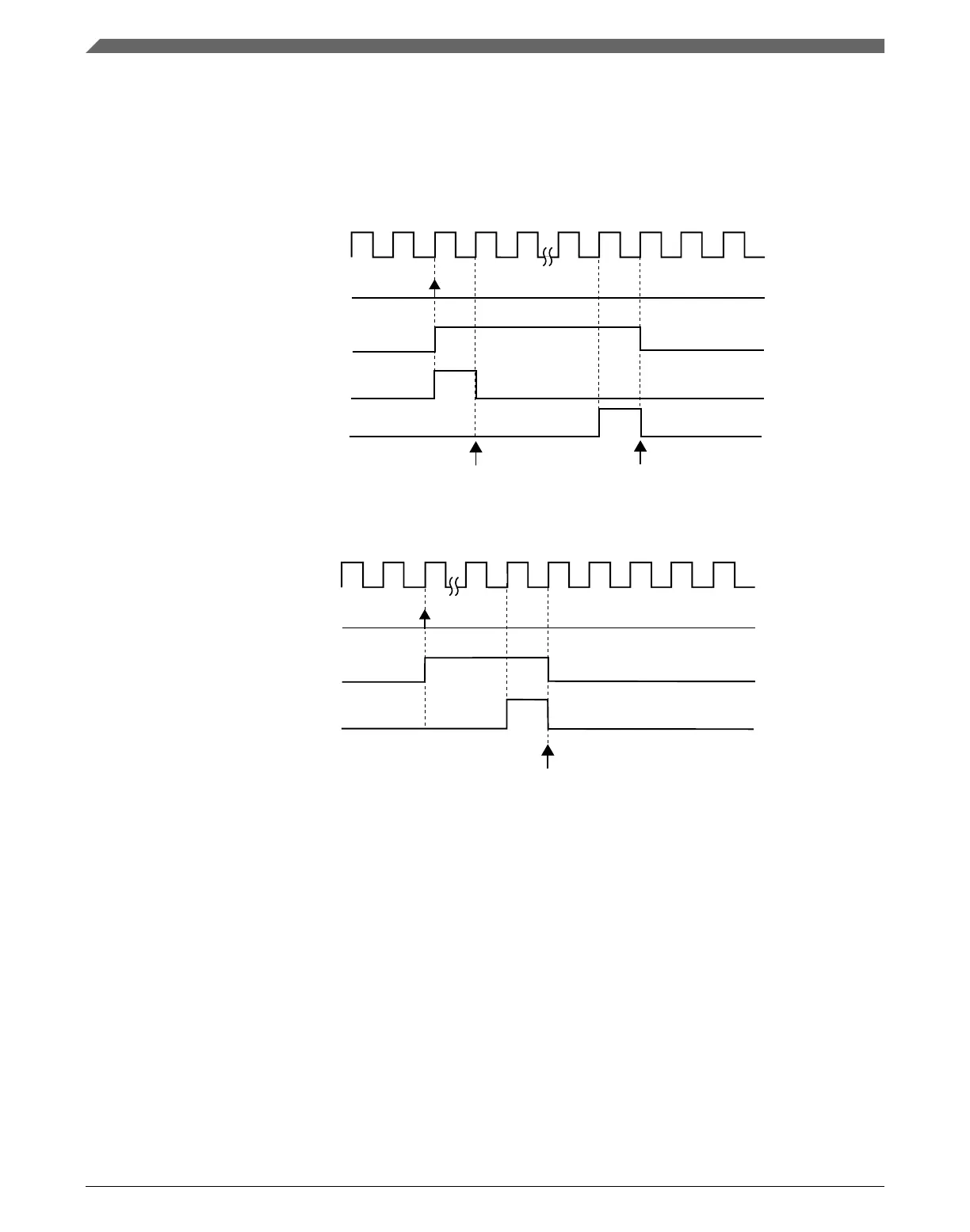

system clock

write 1 to TRIG0 bit

TRIG0 bit

trigger 0 event

OUTMASK register is updated and

TRIG0 bit is cleared

Figure 39-54. OUTMASK synchronization with (SYNCMODE = 0), (HWTRIGMODE = 0),

(SYNCHOM = 1), (PWMSYNC = 0), and a hardware trigger was used

If (SYNCMODE = 0), (SYNCHOM = 1), and (PWMSYNC = 1), then this

synchronization is made on the next enabled hardware trigger. The TRIGn bit is cleared

according to Hardware trigger. An example with a hardware trigger follows.

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

982 NXP Semiconductors

Loading...

Loading...