UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 102 of 841

NXP Semiconductors

UM10360

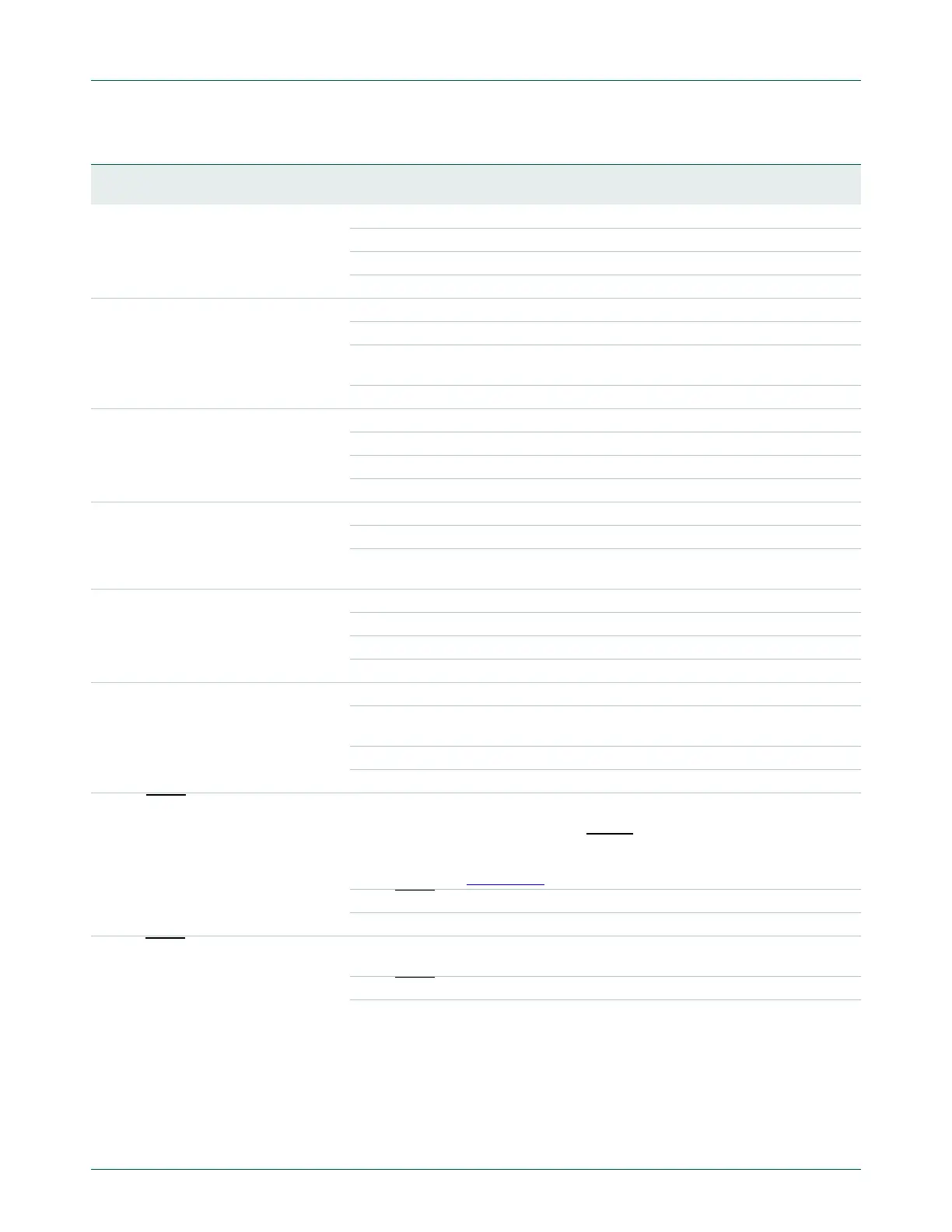

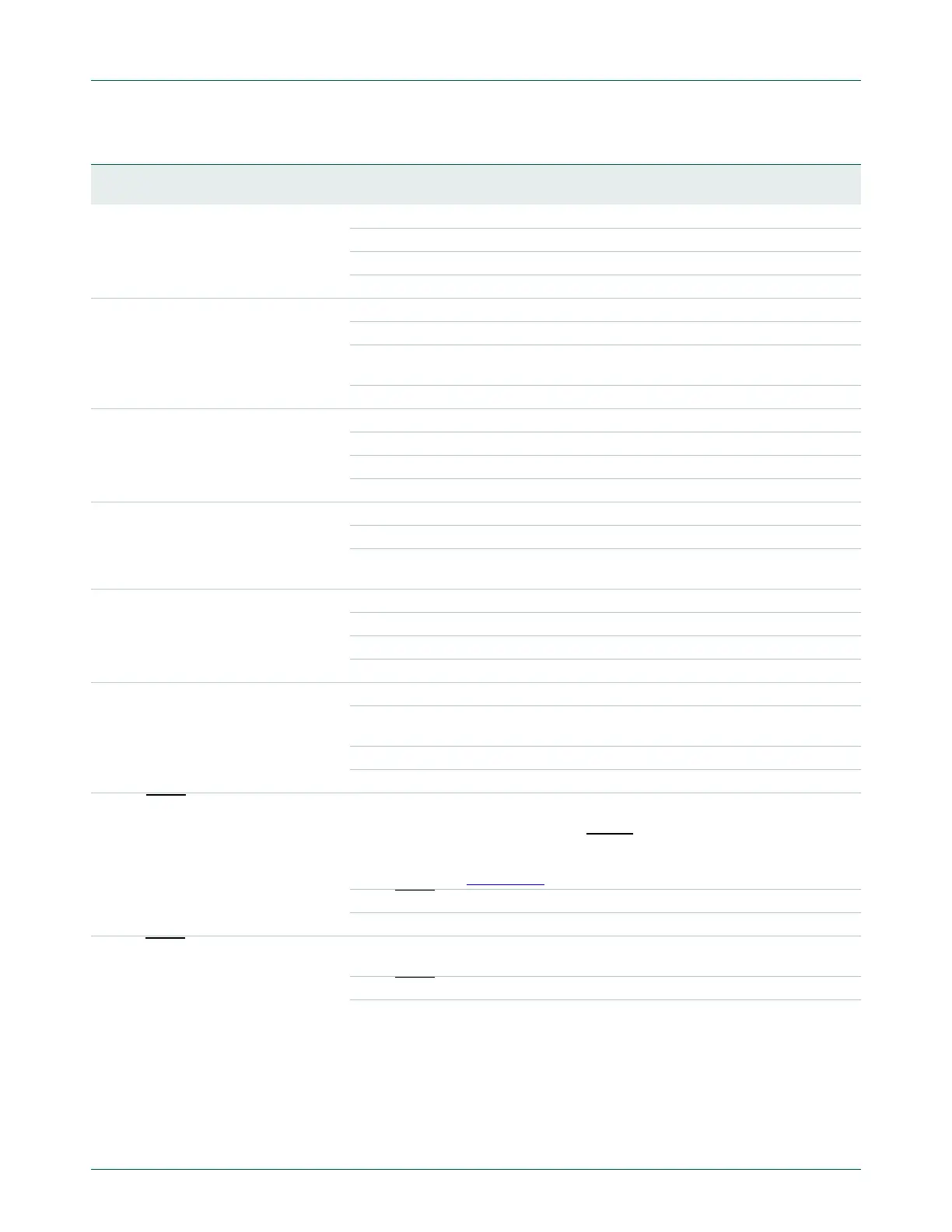

Chapter 7: LPC176x/5x Pin configuration

P2[4] / PWM1[5] /

DSR1 /

TRACEDATA[1]

69 54 I/O P2[4] — General purpose digital input/output pin.

O

PWM1[5] — Pulse Width Modulator 1, channel 5 output.

I

DSR1 — Data Set Ready input for UART1.

O

TRACEDATA[1] — Trace data, bit 1.

P2[5] / PWM1[6] /

DTR1 /

TRACEDATA[0]

68 53 I/O

P2[5] — General purpose digital input/output pin.

O

PWM1[6] — Pulse Width Modulator 1, channel 6 output.

O

DTR1 — Data Terminal Ready output for UART1. Can also be configured

to be an RS-485/EIA-485 output enable signal.

O

TRACEDATA[0] — Trace data, bit 0.

P2[6] / PCAP1[0] /

RI1 / TRACECLK

67 52 I/O

P2[6] — General purpose digital input/output pin.

I

PCAP1[0] — Capture input for PWM1, channel 0.

I

RI1 — Ring Indicator input for UART1.

O

TRACECLK — Trace Clock.

P2[7] / RD2 /

RTS1

66 51 I/O

P2[7] — General purpose digital input/output pin.

I

RD2 — CAN2 receiver input.

O

RTS1 — Request to Send output for UART1. Can also be configured to be

an RS-485/EIA-485 output enable signal.

P2[8] / TD2 /

TXD2 / ENET_MDC

65 50 I/O

P2[8] — General purpose digital input/output pin.

O

TD2 — CAN2 transmitter output.

O

TXD2 — Transmitter output for UART2.

O

ENET_MDC — Ethernet MIIM clock.

P2[9] /

USB_CONNECT /

RXD2 /

ENET_MDIO

64 49 I/O

P2[9] — General purpose digital input/output pin.

O

USB_CONNECT — Signal used to switch an external 1.5 k resistor

under software control. Used with the SoftConnect USB feature.

I

RXD2 — Receiver input for UART2.

I/O

ENET_MDIO — Ethernet MIIM data input and output.

P2[10] / EINT0

/

NMI

53 41 I/O P2[10] — General purpose digital input/output pin. 5 V tolerant pad with 5

ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

Note: A LOW on this pin while RESET is LOW forces the on-chip

bootloader to take over control of the part after a reset and go into ISP

mode. See Section 32.1

.

I

EINT0 — External interrupt 0 input.

I

NMI — Non-maskable interrupt input.

P2[11] / EINT1

/

I2STX_CLK

52 - I/O P2[11] — General purpose digital input/output pin. 5 V tolerant pad with 5

ns glitch filter providing digital I/O functions with TTL levels and hysteresis.

I

EINT1 — External interrupt 1 input.

I/O

I2STX_CLK — Transmit Clock. It is driven by the master and received by

the slave. Corresponds to the signal SCK in the

I

2

S-bus specification.

Table 73. Pin description …continued

Symbol LQFP

100

LQFP

80

Type Description

Loading...

Loading...