UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 126 of 841

NXP Semiconductors

UM10360

Chapter 9: LPC176x/5x General Purpose Input/Output (GPIO)

Access to a port pin via the FIOxSET register is conditioned by the corresponding bit of

the FIOxMASK register (see Section 9.5.5

).

Aside from the 32-bit long and word only accessible FIOxSET register, every fast GPIO

port can also be controlled via several byte and half-word accessible registers listed in

Table 106

, too. Next to providing the same functions as the FIOxSET register, these

additional registers allow easier and faster access to the physical port pins.

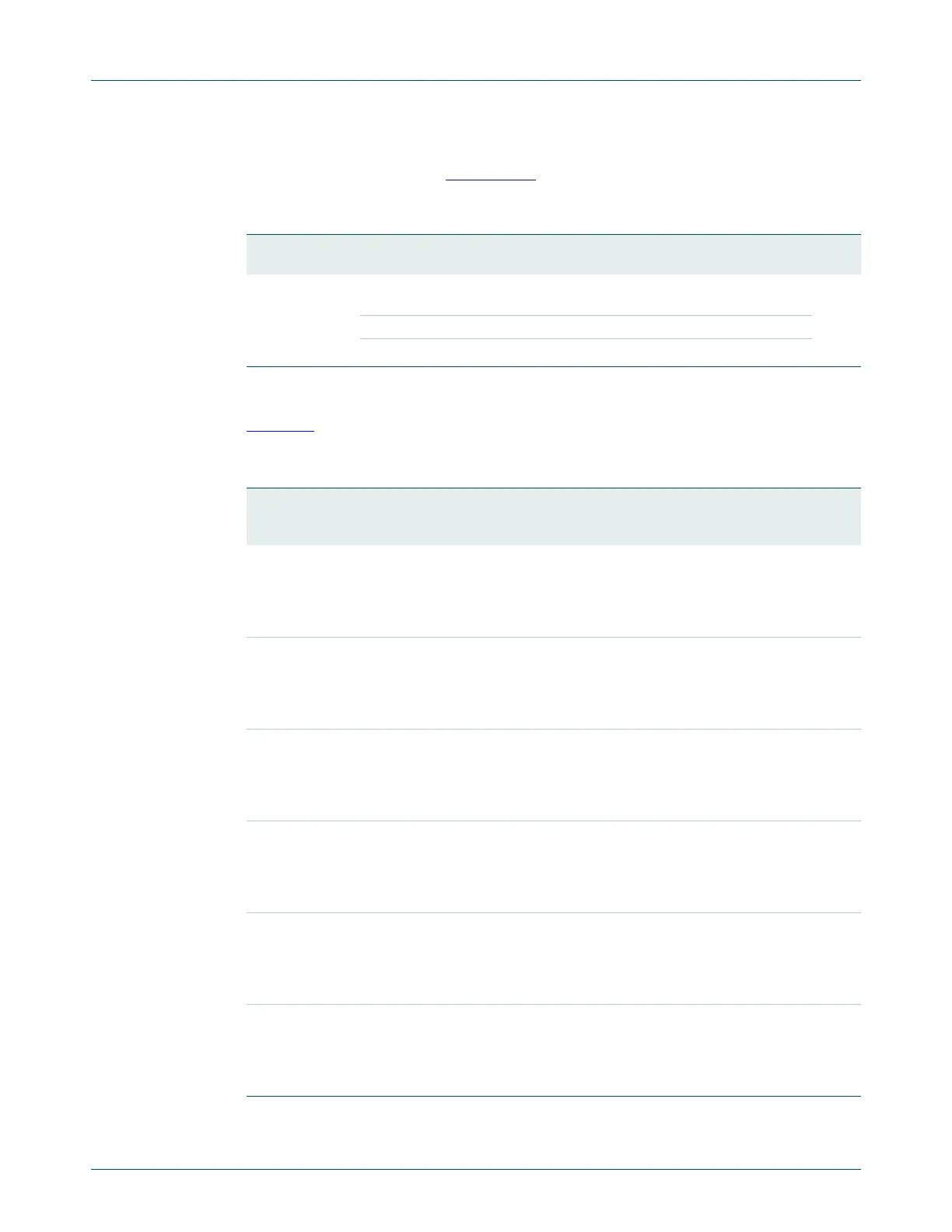

Table 105. Fast GPIO port output Set register (FIO0SET to FIO4SET - addresses 0x2009 C018

to 0x2009 C098) bit description

Bit Symbol Value Description Reset

value

31:0 FIO0SET

FIO1SET

FIO2SET

FIO3SET

FIO4SET

Fast GPIO output value Set bits. Bit 0 in FIOxSET controls pin

Px.0, bit 31 in FIOxSET controls pin Px.31.

0x0

0 Controlled pin output is unchanged.

1 Controlled pin output is set to HIGH.

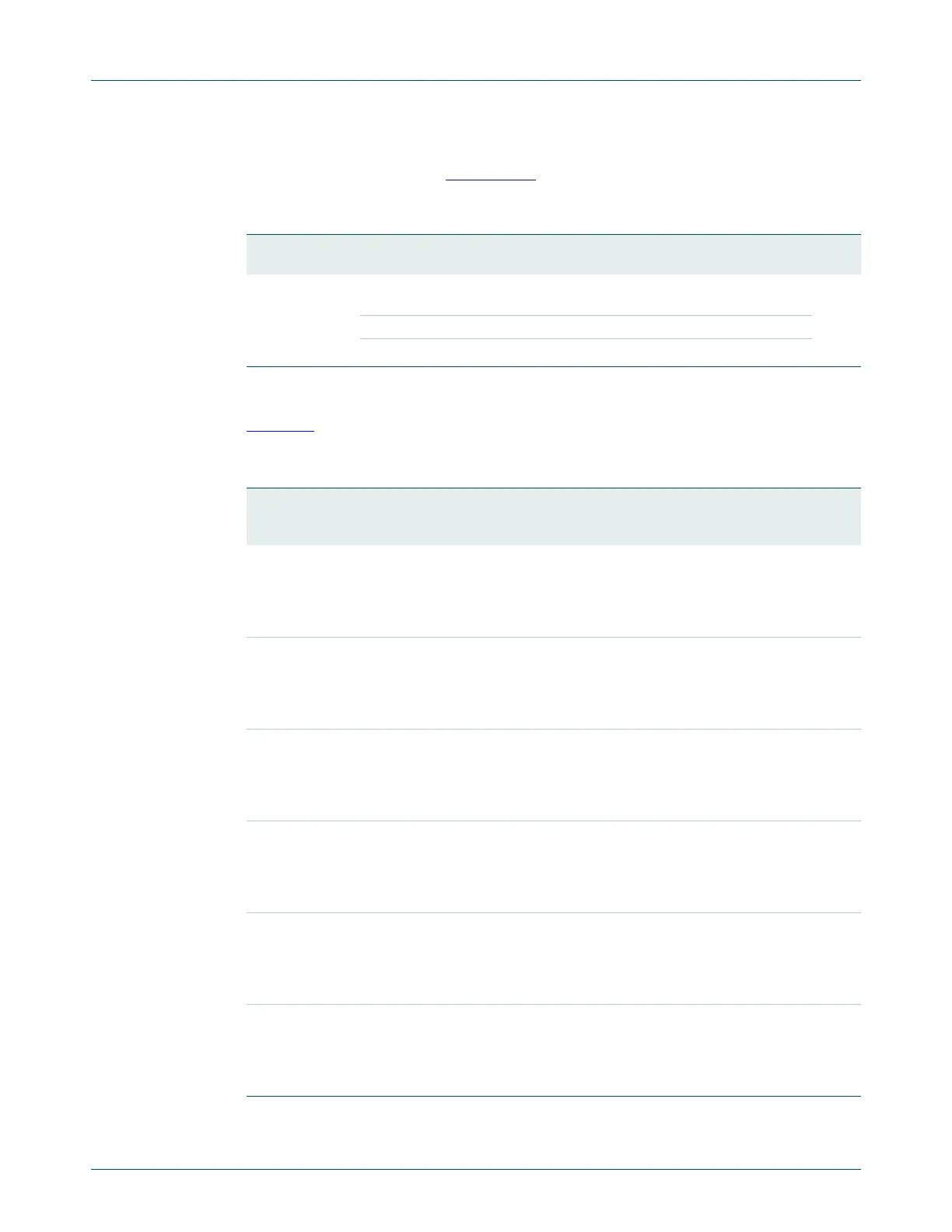

Table 106. Fast GPIO port output Set byte and half-word accessible register description

Generic

Register

name

Description Register

length (bits)

& access

Reset

value

PORTn Register

Address & Name

FIOxSET0 Fast GPIO Port x output Set

register 0. Bit 0 in FIOxSET0

register corresponds to pin

Px.0 … bit 7 to pin Px.7.

8 (byte)

R/W

0x00 FIO0SET0 - 0x2009 C018

FIO1SET0 - 0x2009 C038

FIO2SET0 - 0x2009 C058

FIO3SET0 - 0x2009 C078

FIO4SET0 - 0x2009 C098

FIOxSET1 Fast GPIO Port x output Set

register 1. Bit 0 in FIOxSET1

register corresponds to pin

Px.8 … bit 7 to pin Px.15.

8 (byte)

R/W

0x00 FIO0SET1 - 0x2009 C019

FIO1SET1 - 0x2009 C039

FIO2SET1 - 0x2009 C059

FIO3SET1 - 0x2009 C079

FIO4SET1 - 0x2009 C099

FIOxSET2 Fast GPIO Port x output Set

register 2. Bit 0 in FIOxSET2

register corresponds to pin

Px.16 … bit 7 to pin Px.23.

8 (byte)

R/W

0x00 FIO0SET2 - 0x2009 C01A

FIO1SET2 - 0x2009 C03A

FIO2SET2 - 0x2009 C05A

FIO3SET2 - 0x2009 C07A

FIO4SET2 - 0x2009 C09A

FIOxSET3 Fast GPIO Port x output Set

register 3. Bit 0 in FIOxSET3

register corresponds to pin

Px.24 … bit 7 to pin Px.31.

8 (byte)

R/W

0x00 FIO0SET3 - 0x2009 C01B

FIO1SET3 - 0x2009 C03B

FIO2SET3 - 0x2009 C05B

FIO3SET3 - 0x2009 C07B

FIO4SET3 - 0x2009 C09B

FIOxSETL Fast GPIO Port x output Set

Lower half-word register. Bit 0

in FIOxSETL register

corresponds to pin Px.0 … bit

15 to pin Px.15.

16 (half-word)

R/W

0x0000 FIO0SETL - 0x2009 C018

FIO1SETL - 0x2009 C038

FIO2SETL - 0x2009 C058

FIO3SETL - 0x2009 C078

FIO4SETL - 0x2009 C098

FIOxSETU Fast GPIO Port x output Set

Upper half-word register. Bit 0

in FIOxSETU register

corresponds to Px.16 … bit

15 to Px.31.

16 (half-word)

R/W

0x0000 FIO0SETU - 0x2009 C01A

FIO1SETU - 0x2009 C03A

FIO2SETU - 0x2009 C05A

FIO3SETU - 0x2009 C07A

FIO4SETU - 0x2009 C09A

Loading...

Loading...