UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 356 of 841

NXP Semiconductors

UM10360

Chapter 16: LPC176x/5x CAN1/2

[1] After reading all messages and releasing their memory space with the command 'Release Receive Buffer,' this bit is cleared.

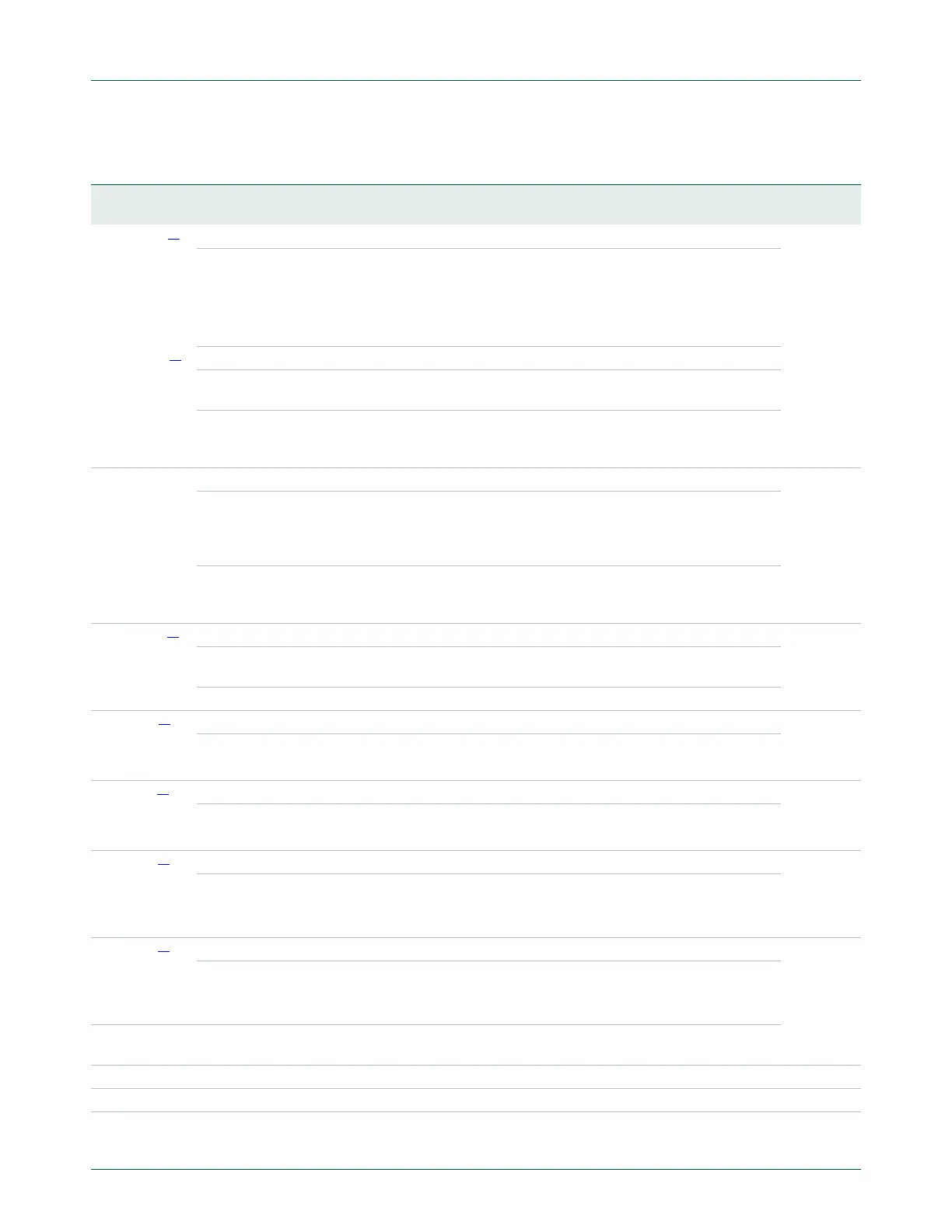

Table 319. CAN Global Status Register (CAN1GSR - address 0x4004 4008, CAN2GSR - address 0x4004 8008) bit

description

Bit Symbol Value Function Reset

Value

RM

Set

0RBS

[1]

Receive Buffer Status. 0 0

0 (empty) No message is available.

1 (full) At least one complete message is received by the Double Receive Buffer

and available in the CANxRFS, CANxRID, and if applicable the CANxRDA

and CANxRDB registers. This bit is cleared by the Release Receive Buffer

command in CANxCMR, if no subsequent received message is available.

1DOS

[2]

Data Overrun Status. 0 0

0 (absent) No data overrun has occurred since the last Clear Data Overrun command

was given/written to CANxCMR (or since Reset).

1 (overrun) A message was lost because the preceding message to this CAN controller

was not read and released quickly enough (there was not enough space for

a new message in the Double Receive Buffer).

2 TBS Transmit Buffer Status. 1 1

0 (locked) At least one of the Transmit Buffers is not available for the CPU, i.e. at least

one previously queued message for this CAN controller has not yet been

sent, and therefore software should not write to the CANxTFI, CANxTID,

CANxTDA, nor CANxTDB registers of that (those) Tx buffer(s).

1 (released) All three Transmit Buffers are available for the CPU. No transmit message is

pending for this CAN controller (in any of the 3 Tx buffers), and software may

write to any of the CANxTFI, CANxTID, CANxTDA, and CANxTDB registers.

3TCS

[3]

Transmit Complete Status. 1 x

0 (incomplete) At least one requested transmission has not been successfully completed

yet.

1 (complete) All requested transmission(s) has (have) been successfully completed.

4RS

[4]

Receive Status. 1 0

0 (idle) The CAN controller is idle.

1 (receive) The CAN controller is receiving a message.

5TS

[4]

Transmit Status. 1 0

0 (idle) The CAN controller is idle.

1 (transmit) The CAN controller is sending a message.

6ES

[5]

Error Status. 0 0

0 (ok) Both error counters are below the Error Warning Limit.

1 (error) One or both of the Transmit and Receive Error Counters has reached the

limit set in the Error Warning Limit register.

7BS

[6]

Bus Status. 0 0

0 (Bus-On) The CAN Controller is involved in bus activities

1 (Bus-Off) The CAN controller is currently not involved/prohibited from bus activity

because the Transmit Error Counter reached its limiting value of 255.

15:8 - - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

23:16 RXERR - The current value of the Rx Error Counter (an 8-bit value). 0 X

31:24 TXERR - The current value of the Tx Error Counter (an 8-bit value). 0 X

Loading...

Loading...