UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 488 of 841

NXP Semiconductors

UM10360

Chapter 20: LPC176x/5x I2S

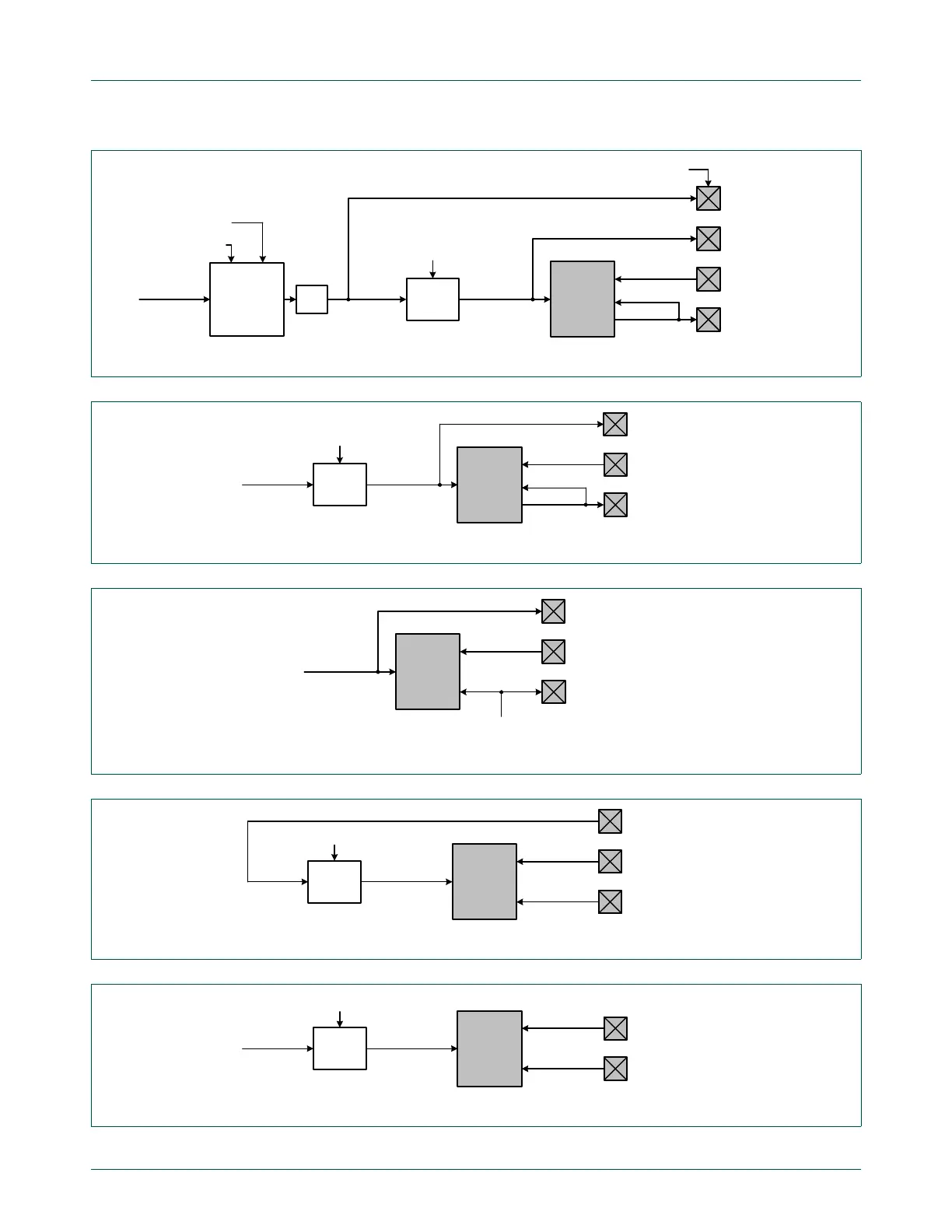

Fig 107. Typical receiver master mode, with or without MCLK output

I2SRXMODE[3]

I2S_PCLK

÷N

(1 to 64)

8-bit

Fractional

Rate Divider

÷2

XY

I2SRX_MCLK

I

2

S

peripheral

block

(receive)

I2SRXBITRATE[5:0]

I2SRX_WS

I2SRX_SDA

I2SRX_CLK

RX_REF RX bit clock

I2SRX_RATE[7:0]

I2SRX_RATE[15:8]

(Pin OE)

RX_WS ref

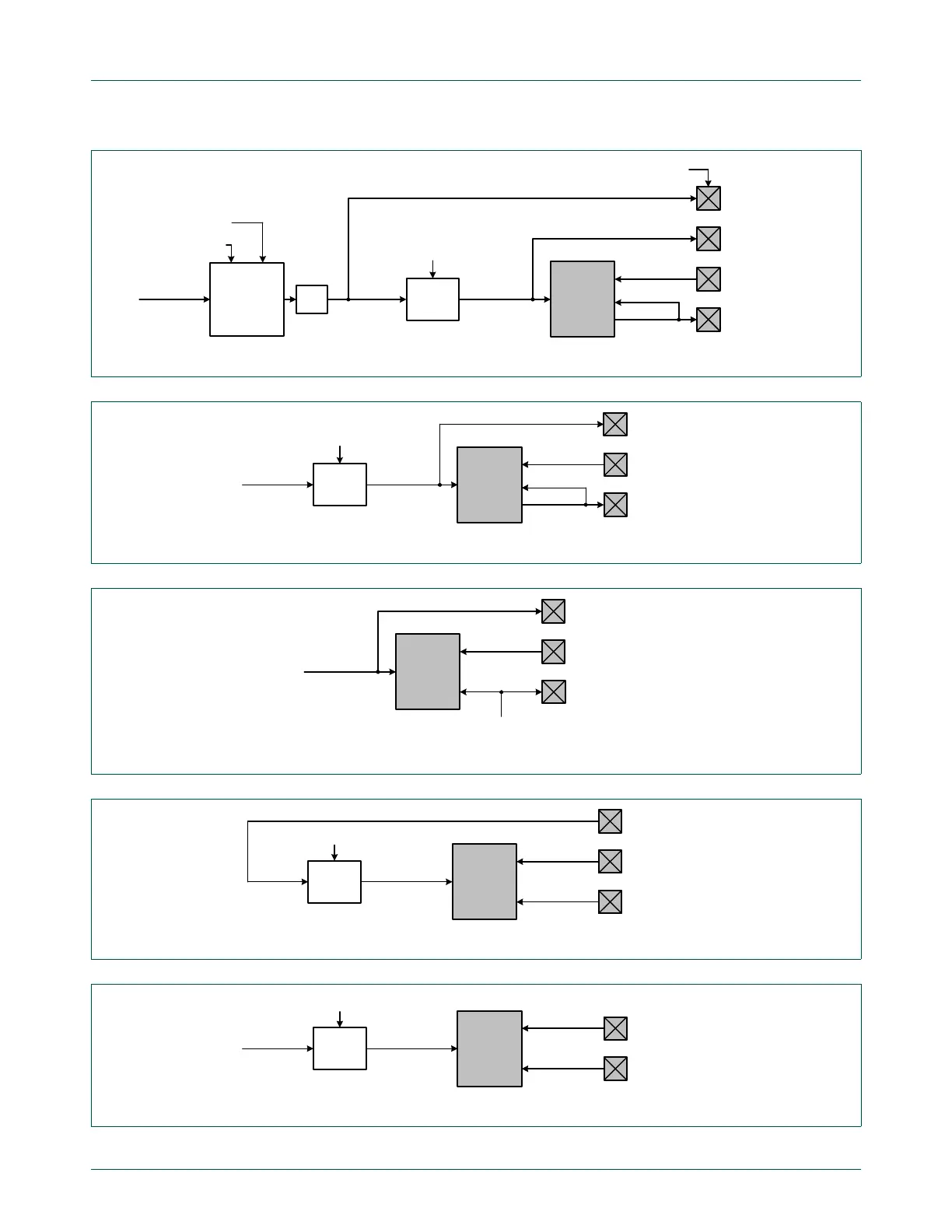

Fig 108. Receiver master mode sharing the transmitter reference clock

÷N

(1 to 64)

I2SRXBITRATE[5:0]

I2SRX_WS

I2SRX_SDA

I2SRX_CLK

TX_REF RX bit clock

RX_WS ref

I

2

S

peripheral

block

(receive)

Fig 109. 4-wire receiver master mode sharing the transmitter bit clock and WS

I2SRX_WS

I2SRX_SDA

I2SRX_CLK

TX bit clock

TX_WS ref

I

2

S

peripheral

block

(receive)

Fig 110. Typical receiver slave mode

÷N

(1 to 64)

I

2

S

peripheral

block

(receive)

I2SRXBITRATE[5:0]

I2SRX_WS

I2SRX_SDA

I2SRX_CLK

RX_REF RX bit clock

Fig 111. Receiver slave mode sharing the transmitter reference clock

÷N

(1 to 64)

I

2

S

peripheral

block

(receive)

I2SRXBITRATE[5:0]

I2SRX_WS

I2SRX_SDA

TX_REF RX bit clock

Loading...

Loading...