UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 93 of 841

NXP Semiconductors

UM10360

Chapter 7: LPC176x/5x Pin configuration

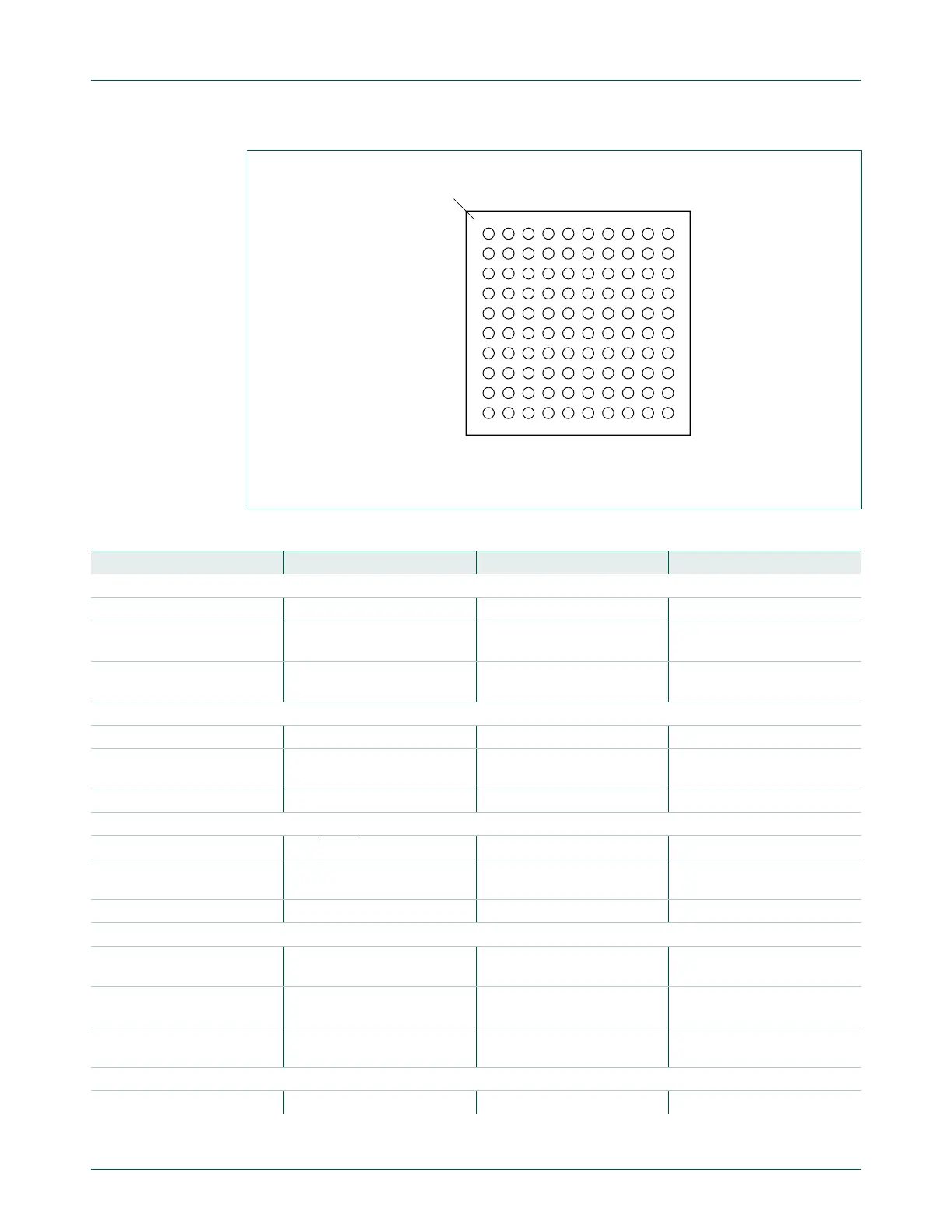

Fig 16. Pin configuration TFBGA100 package

002aaf723

LPC1768FET100

Transparent top view

J

G

K

H

F

E

D

C

B

A

24681013579

ball A1

index area

Table 72. Pin allocation table TFBGA100 package

Pin Symbol Pin Symbol Pin Symbol Pin Symbol

Row A

1 TDO/SWO 2 P0[3]/RXD0/AD0[6] 3 V

DD(3V3)

4 P1[4]/ENET_TX_EN

5 P1[10]/ENET_RXD1 6 P1[16]/ENET_MDC 7 V

DD(REG)(3V3)

8 P0[4]/I2SRX_CLK/

RD2/CAP2[0]

9 P0[7]/I2STX_CLK/

SCK1/MAT2[1]

10 P0[9]/I2STX_SDA/

MOSI1/MAT2[3]

11 - 12 -

Row B

1 TMS/SWDIO 2 RTCK 3 V

SS

4 P1[1]/ENET_TXD1

5 P1[9]/ENET_RXD0 6 P1[17]/

ENET_MDIO

7V

SS

8 P0[6]/I2SRX_SDA/

SSEL1/MAT2[0]

9 P2[0]/PWM1[1]/TXD1 10 P2[1]/PWM1[2]/RXD1 11 - 12 -

Row C

1TCK/SWDCLK 2TRST 3 TDI 4 P0[2]/TXD0/AD0[7]

5 P1[8]/ENET_CRS 6 P1[15]/

ENET_REF_CLK

7 P4[28]/RX_MCLK/

MAT2[0]/TXD3

8 P0[8]/I2STX_WS/

MISO1/MAT2[2]

9V

SS

10 V

DD(3V3)

11 - 12 -

Row D

1 P0[24]/AD0[1]/

I2SRX_WS/CAP3[1]

2 P0[25]/AD0[2]/

I2SRX_SDA/TXD3

3 P0[26]/AD0[3]/

AOUT/RXD3

4n.c.

5 P1[0]/ENET_TXD0 6 P1[14]/ENET_RX_ER 7 P0[5]/I2SRX_WS/

TD2/CAP2[1]

8 P2[2]/PWM1[3]/

CTS1/TRACEDATA[3]

9 P2[4]/PWM1[5]/

DSR1/TRACEDATA[1]

10 P2[5]/PWM1[6]/

DTR1/TRACEDATA[0]

11 - 12 -

Row E

1V

SSA

2V

DDA

3 VREFP 4 n.c.

Loading...

Loading...