RM0444 Rev 5 1221/1390

RM0444 FD controller area network (FDCAN)

1261

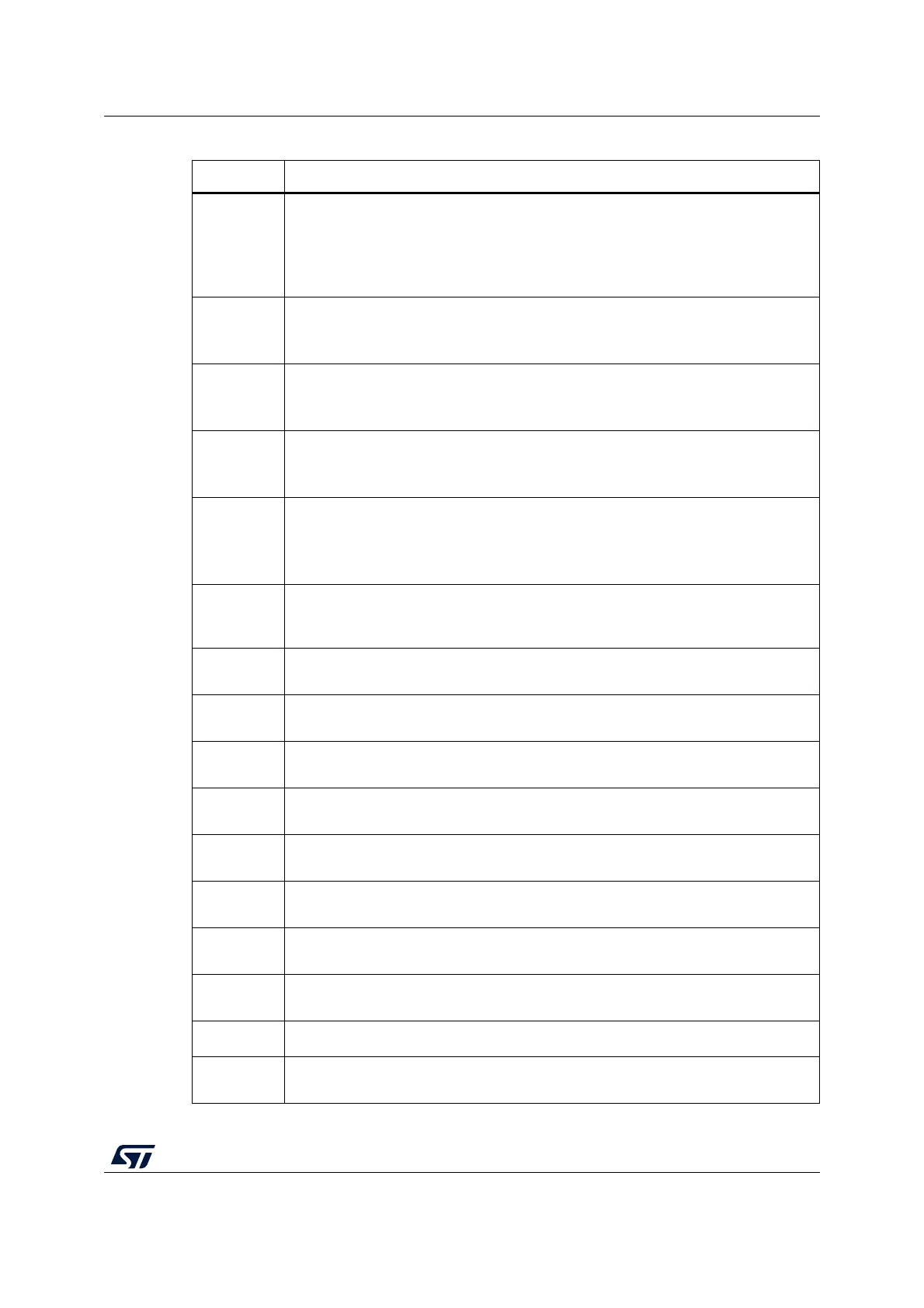

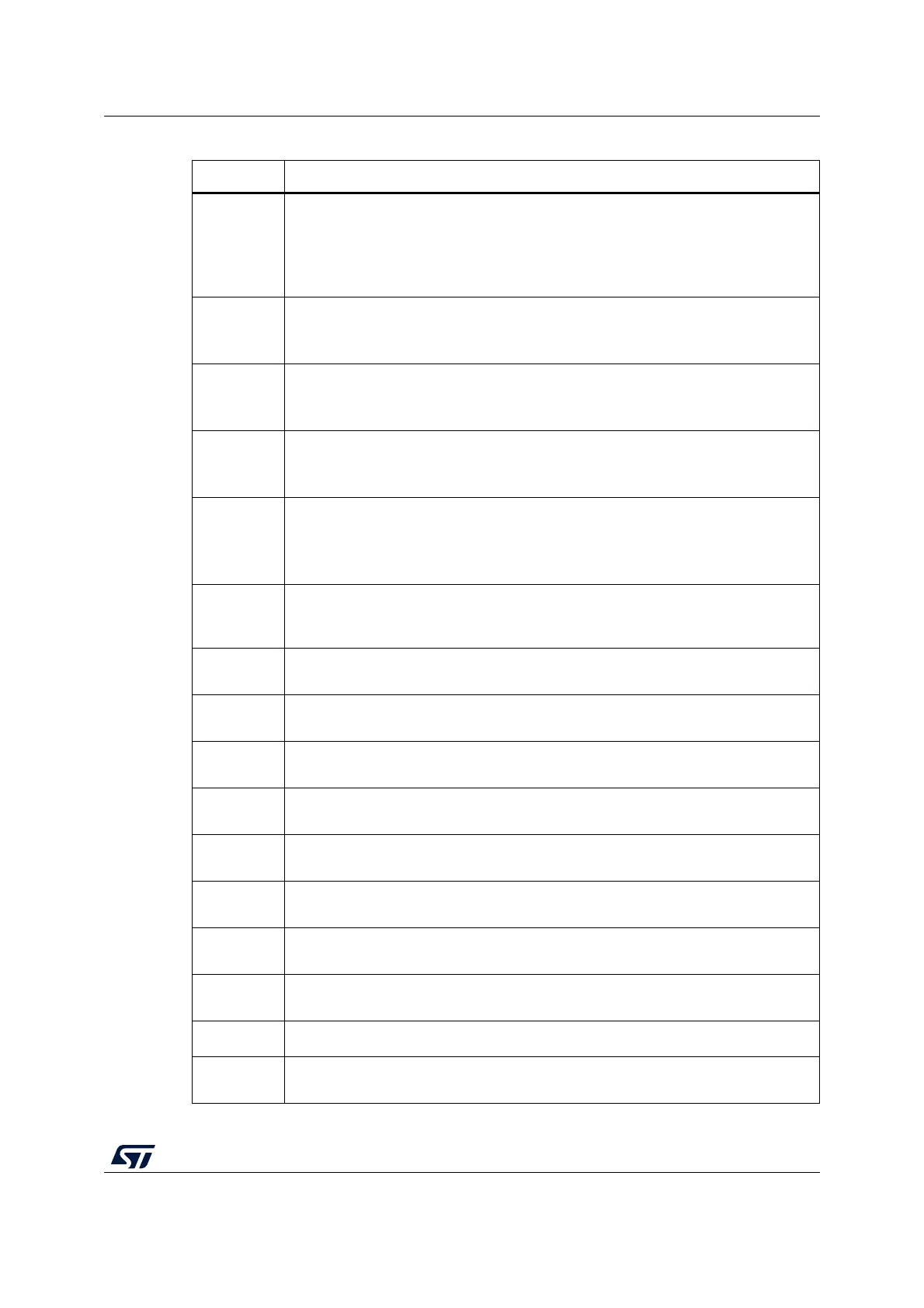

R1 Bit 31

ANMF

Accepted non-matching frame

Acceptance of non-matching frames may be enabled via RXGFC[ANFS] and

RXGFC[ANFE].

– 0: Received frame matching filter index FIDX

– 1: Received frame did not match any Rx filter element

R1 Bits 30:24

FIDX[6:0]

Filter index

0-27=Index of matching Rx acceptance filter element (invalid if ANMF = 1).

Range is 0 to RXGFC[LSS] - 1 or RXGFC[LSE] - 1.

R1 Bit 21

FDF

FD format

– 0: Standard frame format

– 1: FDCAN frame format (new DLC-coding and CRC)

R1 Bit 20

BRS

Bit rate switch

– 0: Frame received without bit rate switching

– 1: Frame received with bit rate switching

R1 Bits 19:16

DLC[3:0]

Data length code

– 0-8: Classic CAN + CAN FD: received frame has 0-8 data bytes

– 9-15: Classic CAN: received frame has 8 data bytes

– 9-15: CAN FD: received frame has 12/16/20/24/32/48/64 data bytes

R1 Bits 15:0

RXTS[15:0]

Rx timestamp

Timestamp Counter value captured on start of frame reception. Resolution depending

on configuration of the Timestamp Counter Prescaler TSCC[TCP].

R2 Bits 31:24

DB3[7:0]

Data Byte 3

R2 Bits 23:16

DB2[7:0]

Data Byte 2

R2 Bits 15:8

DB1[7:0]

Data Byte 1

R2 Bits 7:0

D[7:0]

Data Byte 0

R3 Bits 31:24

DB7[7:0]

Data Byte 7

R3 Bits 23:16

DB6[7:0]

Data Byte 6

R3 Bits 15:8

DB5[7:0]

Data Byte 5

R3 Bits 7:0

DB4[7:0]

Data Byte 4

...

...

Rn Bits 31:24

DBm[7:0]

Data Byte m

Table 206. Rx FIFO element description (continued)

Field Description

Loading...

Loading...