RM0444 Rev 5 1287/1390

RM0444 Universal serial bus full-speed host/device interface (USB)

1307

To avoid spurious clearing of some bits, it is recommended to clear them with a load

instruction where all bits which must not be altered are written with 1, and all bits to be

cleared are written with 0 (these bits can only be cleared by software). Read-modify-write

cycles should be avoided because between the read and the write operations another bit

could be set by the hardware and the next write clears it before the microprocessor has the

time to service the event.

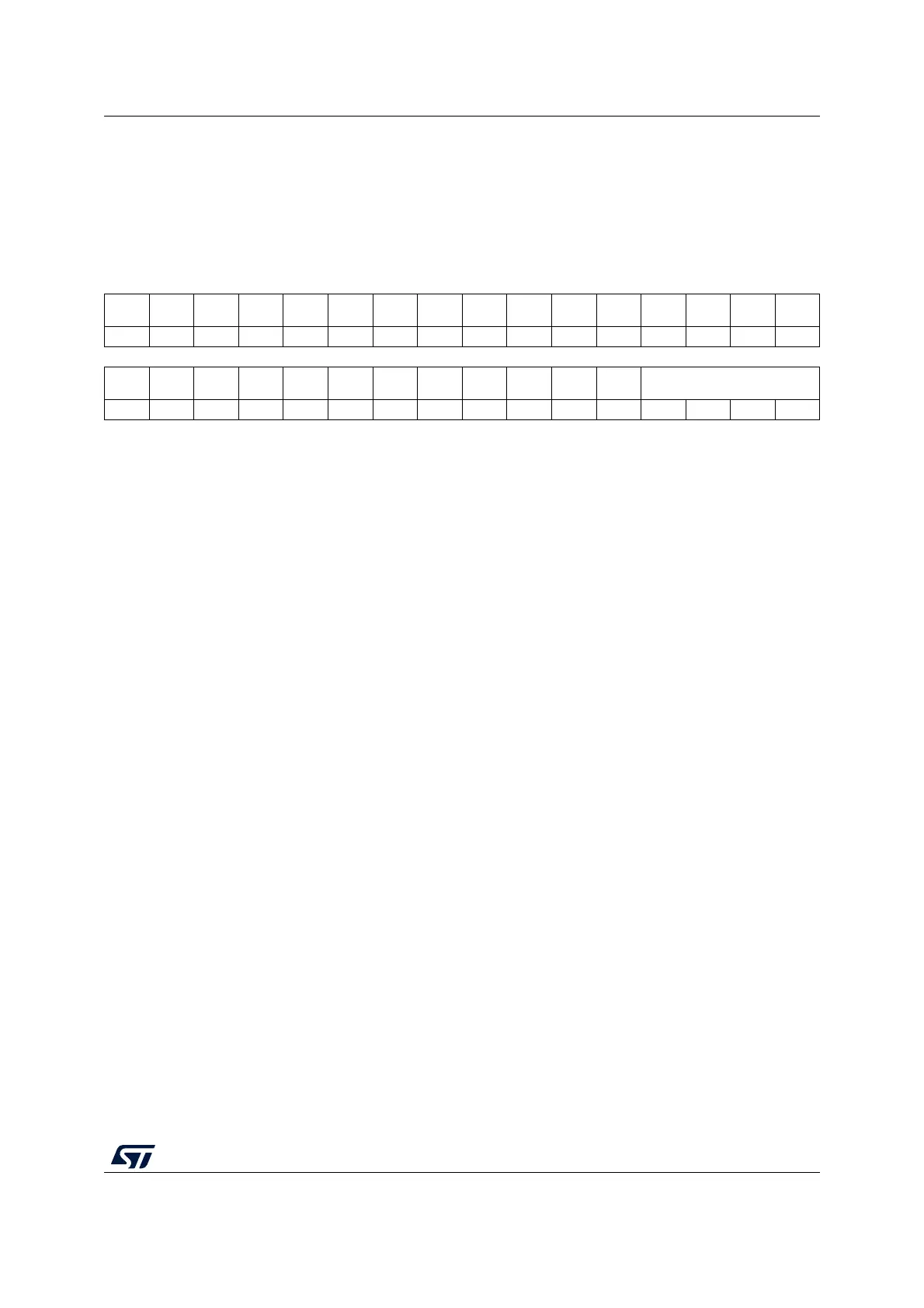

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res.

LS_

DCON

DCON_

STAT

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

THR

512

rr rc_w0

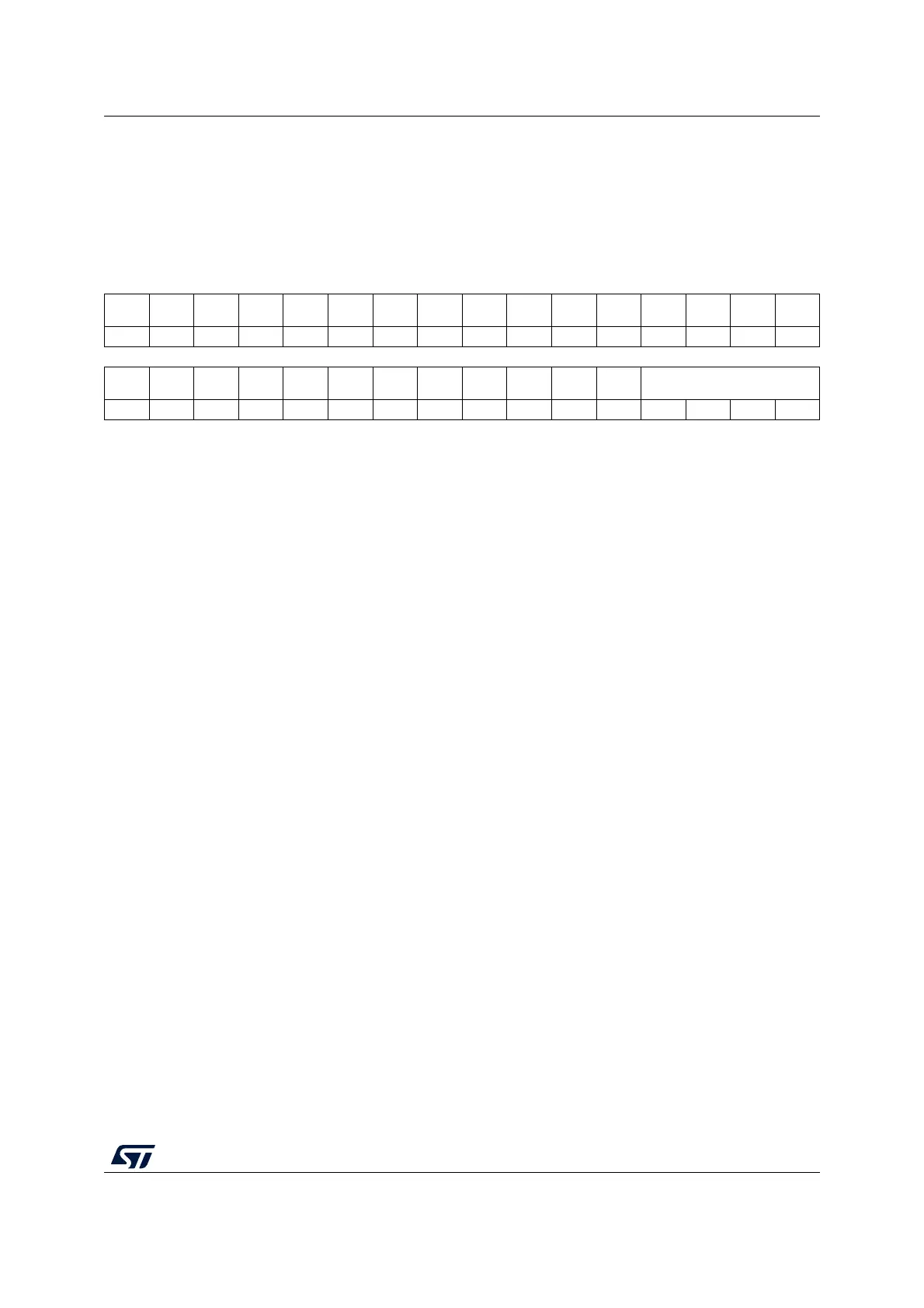

1514131211109876543210

CTR

PMA

OVR

ERR WKUP SUSP

RST_

DCON

SOF ESOF L1REQ Res. Res. DIR IDN[3:0]

rrc_w0rc_w0rc_w0rc_w0rc_w0rc_w0rc_w0rc_w0 rrrrr

Bit 31 Reserved, must be kept at reset value.

Bit 30 LS_DCON: Low speed device connected

– Host mode:

This bit is set by hardware when an LS device connection is detected. Device connection is

signaled after LS J-state is sampled for 22 consecutive cycles of the USB clock (48 MHz)

from the unconnected state.

Bit 29 DCON_STAT: Device connection status

– Host mode:

This bit contains information about device connection status. It is set by hardware when a

LS/FS device is attached to the host while it is reset when the device is disconnected.

0: No device connected

1: FS or LS device connected to the host

Bits 28:17 Reserved, must be kept at reset value.

Bit 16 THR512: 512 byte threshold interrupt

This bit is set to 1 by the hardware when 512 bytes have been transmitted or received during

isochronous transfers. This bit is read/write but only 0 can be written and writing 1 has no

effect. Note that no information is available to indicate the associated channel/endpoint,

however in practice only one ISO endpoint/channel with such large packets can be

supported, so that channel.

Bit 15 CTR: Completed transfer in host mode

This bit is set by the hardware to indicate that an endpoint/channel has successfully

completed a transaction; using DIR and IDN bits software can determine which

endpoint/channel requested the interrupt. This bit is read-only.

Bit 14 PMAOVR: Packet memory area over / underrun

This bit is set if the microcontroller has not been able to respond in time to an USB memory

request. The USB peripheral handles this event in the following way: During reception an

ACK handshake packet is not sent, during transmission a bit-stuff error is forced on the

transmitted stream; in both cases the host retries the transaction. The PMAOVR interrupt

should never occur during normal operations. Since the failed transaction is retried by the

host, the application software has the chance to speed-up device operations during this

interrupt handling, to be ready for the next transaction retry; however this does not happen

during isochronous transfers (no isochronous transaction is anyway retried) leading to a loss

of data in this case. This bit is read/write but only 0 can be written and writing 1 has no effect.

Loading...

Loading...