Reset and clock control (RCC) RM0444

184/1390 RM0444 Rev 5

where f

PLLIN

is the PLL input clock frequency, f

VCO

is the PLL VCO frequency, and P, Q and

R are f

VCO

division factors and f

PLLP

, f

PLLQ

and f

PLLR

the clock frequencies of the PLLPCLK,

PLLQCLK and PLLRCLK PLL clock outputs, respectively.

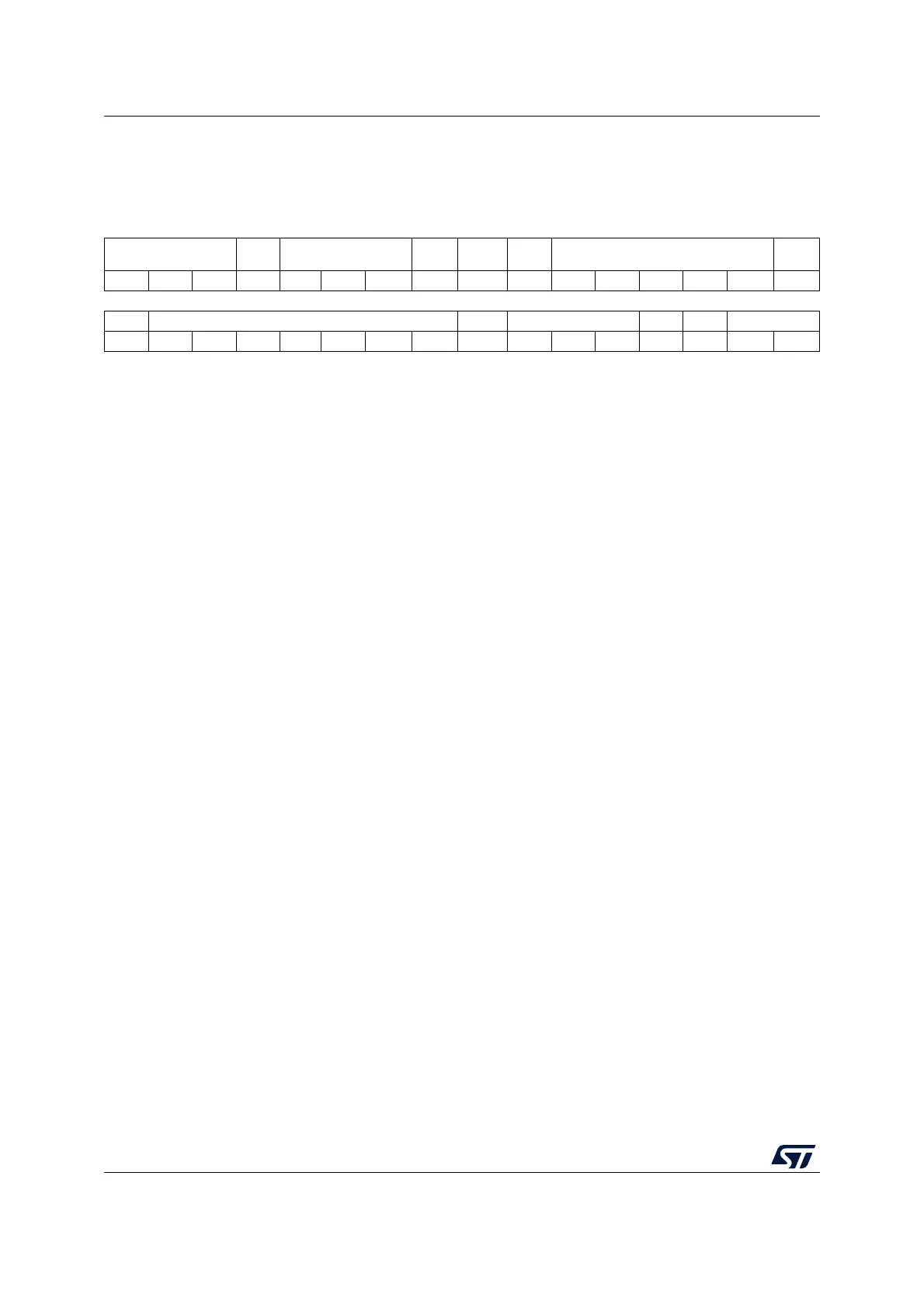

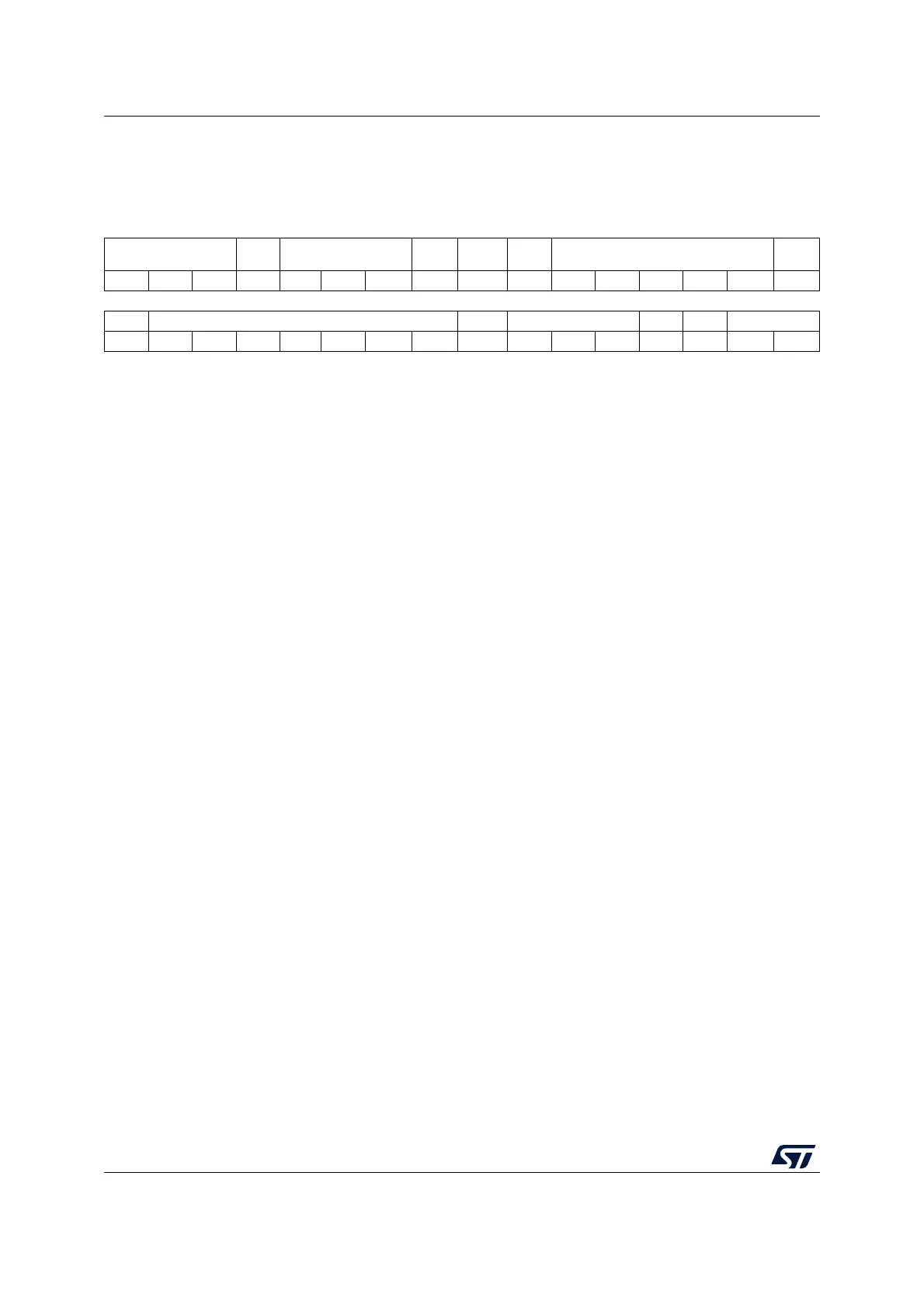

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PLLR[2:0]

PLL

REN

PLLQ[2:0]

PLL

QEN

Res. Res. PLLP[4:0]

PLL

PEN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109 8 7 654321 0

Res. PLLN[7:0] Res. PLLM[2:0] Res. Res. PLLSRC[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:29 PLLR[2:0]: PLL VCO division factor R for PLLRCLK clock output

This bitfield is controlled by software. It sets the PLL VCO division factor R as follows:

000: Reserved

001: 2

010: 3

011: 4

100: 5

101: 6

110: 7

111: 8

The bitfield can be written only when the PLL is disabled.

The PLLRCLK clock can be selected as system clock.

Caution: The software must set this bitfield so as not to exceed 64 MHz on this clock.

Bit 28 PLLREN: PLLRCLK clock output enable

This bit is controlled by software to enable/disable the PLLRCLK clock output of the PLL:

0: Disable

1: Enable

This bit cannot be written when PLLRCLK output of the PLL is selected for system clock.

Disabling the PLLRCLK clock output, when not used, allows saving power.

Bits 27:25 PLLQ[2:0]: PLL VCO division factor Q for PLLQCLK clock output

This bitfield is controlled by software. It sets the PLL VCO division factor Q as follows:

000: Reserved

001: 2

010: 3

011: 4

100: 5

101: 6

110: 7

111: 8

The bitfield can be written only when the PLL is disabled.

Caution: The software must set this bitfield so as not to exceed 128 MHz on this clock.

Bit 24 PLLQEN: PLLQCLK clock output enable

This bit is controlled by software to enable/disable the PLLQCLK clock output of the PLL:

0: Disable

1: Enable

Disabling the PLLQCLK clock output, when not used, allows saving power.

Bits 23:22 Reserved, must be kept at reset value.

Loading...

Loading...