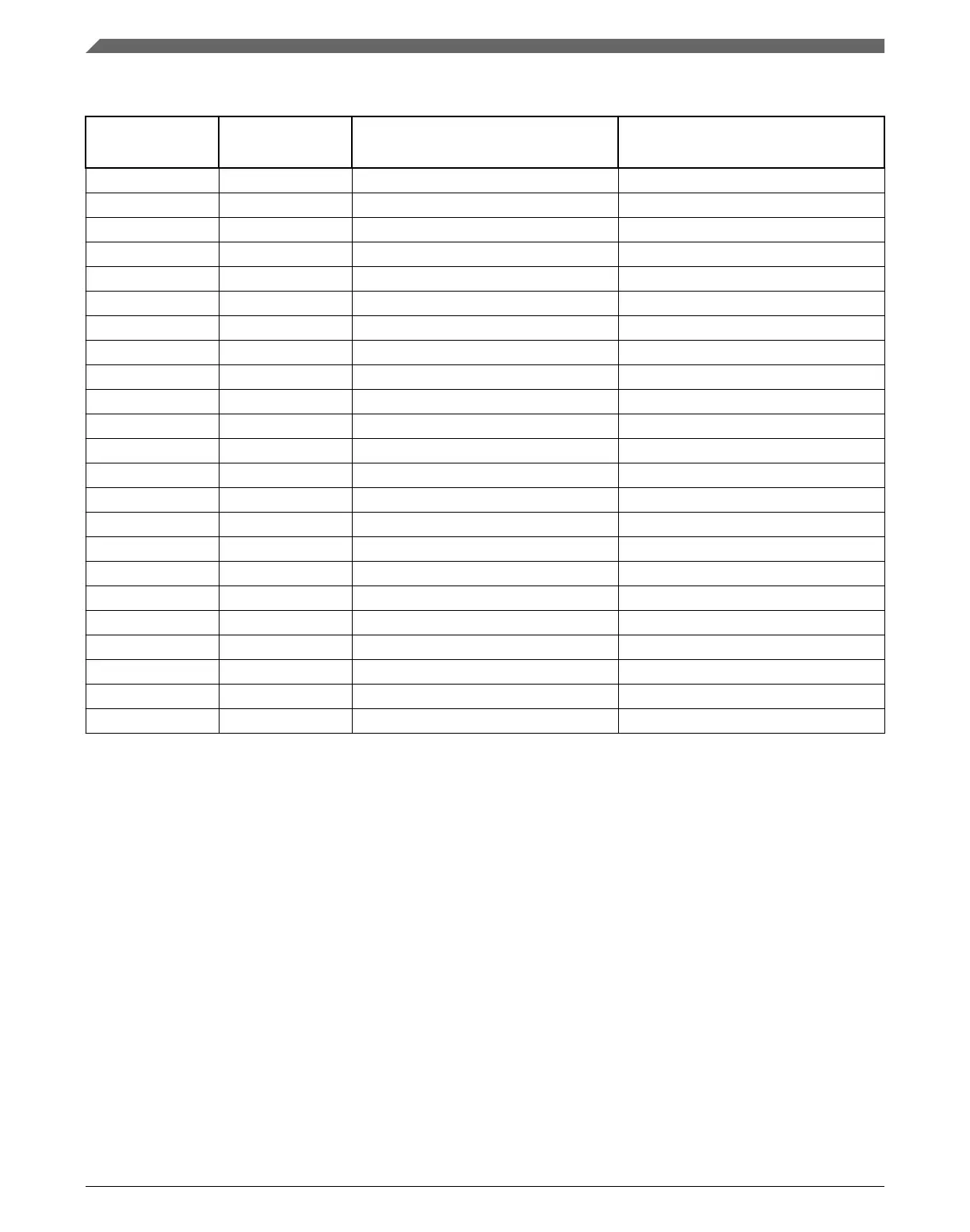

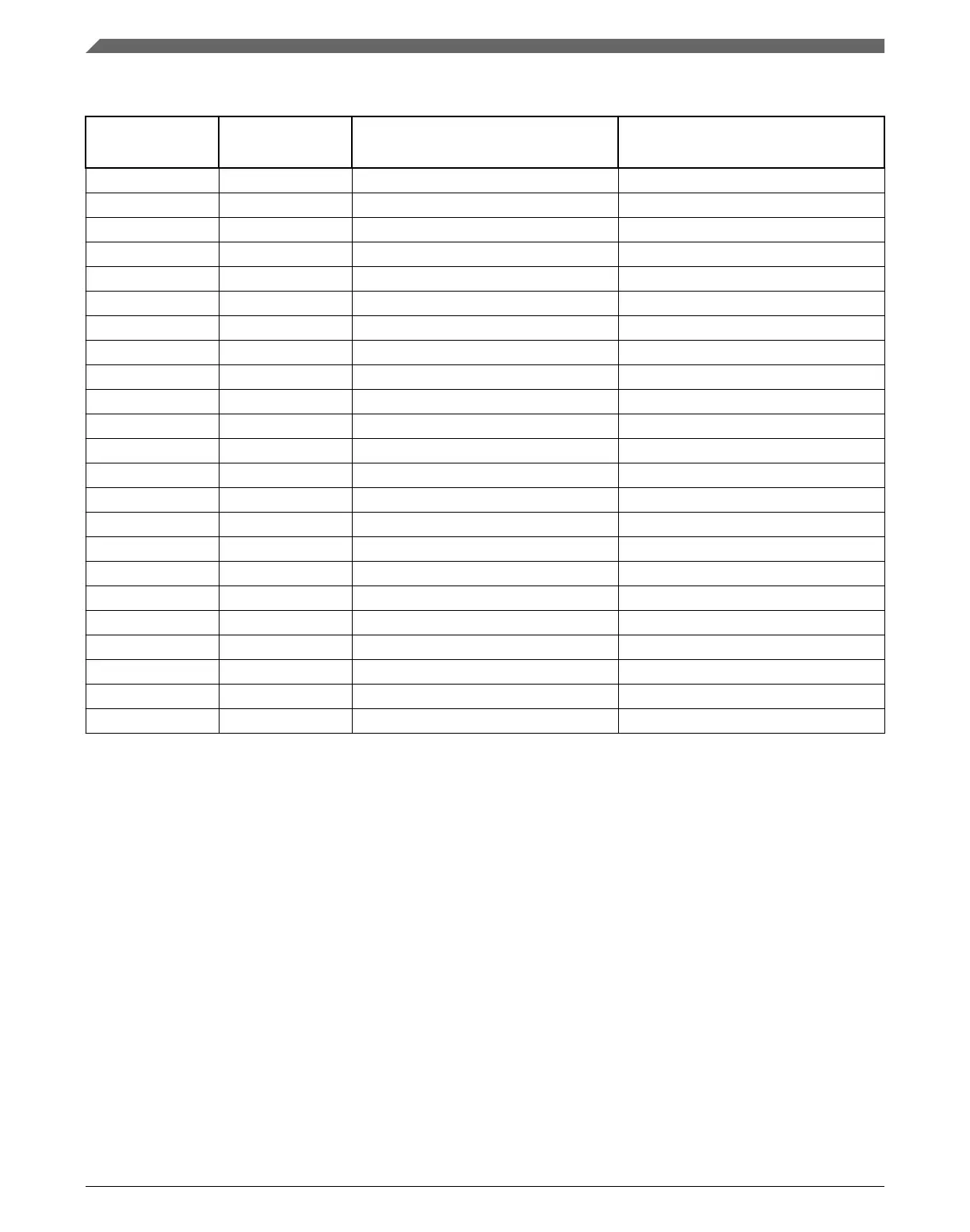

Table 3-42. ADC1 Assignments (continued)

ADC Channel

(SC1n[ADCH])

Channel Input signal (SC1n[DIFF]= 1) Input signal (SC1n[DIFF]= 0)

01001 AD9 Reserved ADC1_SE9

01010 AD10 Reserved Reserved

01011 AD11 Reserved Reserved

01100 AD12 Reserved ADC1_SE12

01101 AD13 Reserved ADC1_SE13

01110 AD14 Reserved ADC1_SE14

01111 AD15 Reserved ADC1_SE15

10000 AD16 Reserved ADC1_SE16

10001 AD17 Reserved ADC1_SE17

10010 AD18 Reserved VREF Output/ADC1_SE18

10011 AD19 Reserved ADC1_DM0

10100 AD20 Reserved ADC1_DM1

10101 AD21 Reserved Reserved

10110 AD22 Reserved VBAT

10111 AD23 Reserved 12-bit DAC1 Output/ADC1_SE23

11000 AD24 Reserved Reserved

11001 AD25 Reserved Reserved

11010 AD26 Temperature Sensor (Diff) Temperature Sensor (S.E)

11011 AD27 Bandgap (Diff)

2

Bandgap (S.E)

2

11100 AD28 Reserved Reserved

11101 AD29 -VREFH (Diff) VREFH (S.E)

11110 AD30 Reserved VREFL

11111 AD31 Module Disabled Module Disabled

1. ADCx_CFG2[MUXSEL] bit selects between ADCx_SEn channels a and b. Refer to MUXSEL description in ADC chapter

for details.

2. This is the PMC bandgap 1V reference voltage and not the VREF module 1.2 V reference voltage. Prior to reading from

this ADC channel, ensure that you enable the bandgap buffer by setting the PMC_REGSC[BGBE] bit. Refer to the device

data sheet for the bandgap voltage (V

BG

) specification.

3.7.1.4 ADC Channels MUX Selection

The following figure shows the assignment of ADCx_SEn channels a and b through a

MUX selection to ADC. To select between alternate set of channels, refer to

ADCx_CFG2[MUXSEL] bit settings for more details.

Analog

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

100 NXP Semiconductors

Loading...

Loading...