28.5.4.1.1 Execute-only Access Register High (x_XACCH)

The execute-only access register is a 64-bit register that is implemented as two 32-bit

registers.

•

High execute-only access bits (segments 63-32) are contained in x_XACCH.

•

Low execute-only access bits (segments 31-0) are contained in x_XACCL.

The x_XACC{H,L} registers provide a bit map for the flash segments, to allow data read

or execute only or both data and instruction fetches for each associated segment. By

definition, execute-only accesses include instruction fetches or PC-relative data loads

from the processor.

During the reset sequence the XACC register is loaded with a pre-programmed value

from non-volatile space in flash. For more about NVM characteristics, see the functional

description. Any change made to an NVM location takes effect on the next system reset.

The flash basis for the values is signified by x in the reset value.

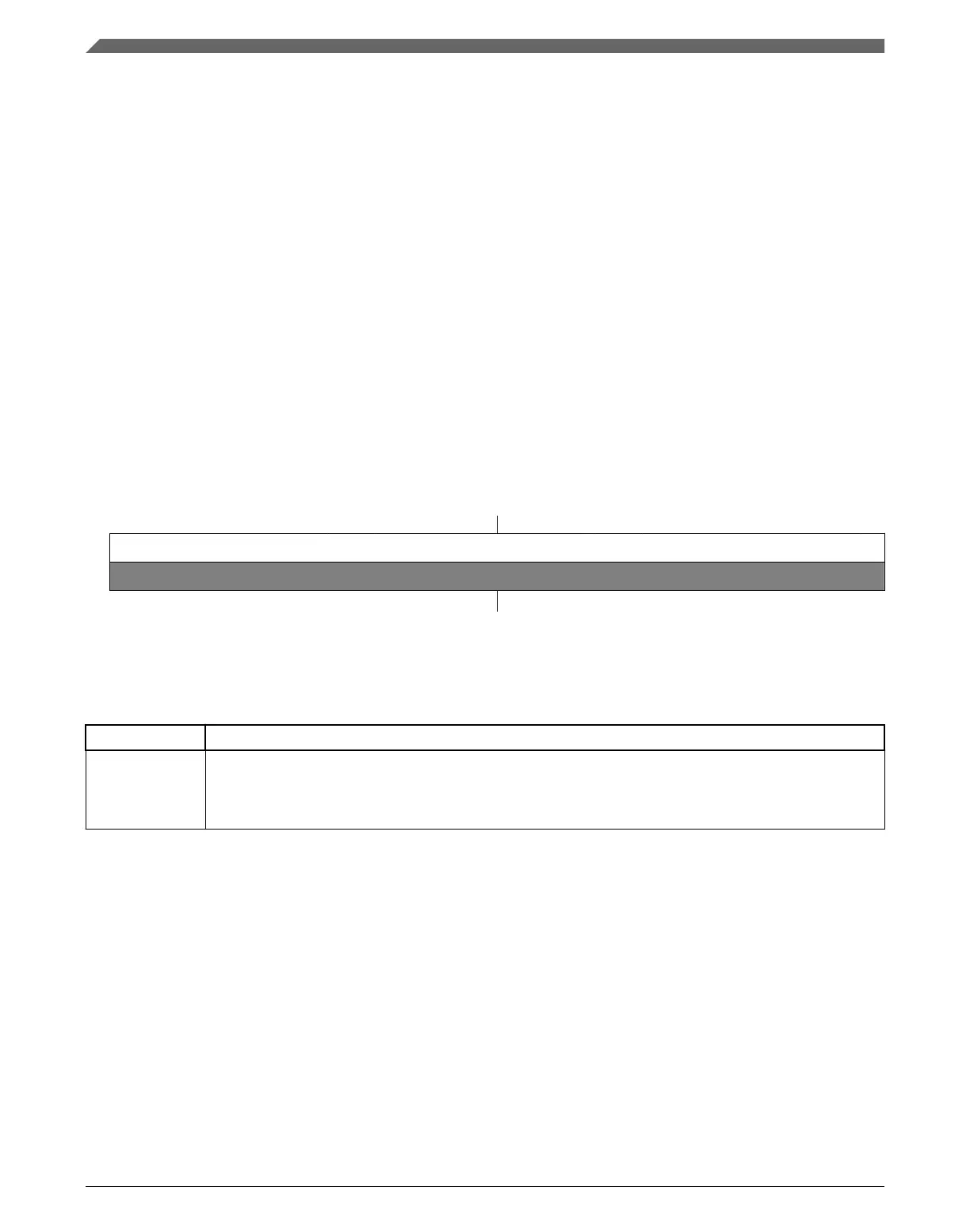

Address:

0h base + 18h offset = 18h

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

XA[63:32]

W

Reset

x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x*

* Notes:

Pre-programmed flash valuex = Undefined at reset.•

x_XACCH field descriptions

Field Description

XA[63:32] Execute-only Access Control for segments 63-32

0 Associated segment is accessible in execute mode only (as an instruction fetch)

1 Associated segment is accessible as data or in execute mode

28.5.4.1.2 Execute-only Access Register Low (x_XACCL)

The XACC{H,L} registers provide a bit map for the flash segments to allow execute only

or both data and instruction fetches for each associated segment. XACCH covers

segments 63-32 and XACCL covers segments 31-0. By definition, execute-only accesses

include instruction fetches or PC-relative data loads from the processor.

During the reset sequence the XACC register is loaded with a pre-programmed value

from non-volatile space in flash. For more about NVM characteristics, see the functional

description. Any change made to an NVM location takes effect on the next system reset.

The flash basis for the values is signified by x in the reset value.

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

618 NXP Semiconductors

Loading...

Loading...