RM0444 Rev 5 1289/1390

RM0444 Universal serial bus full-speed host/device interface (USB)

1307

USB frame number register (USB_FNR)

Address offset: 0x48

Reset value: 0x0000 0XXX (where X is undefined)

Bit 7 L1REQ: LPM L1 state request

– Device mode

This bit is set by the hardware when LPM command to enter the L1 state is successfully

received and acknowledged. This bit is read/write but only 0 can be written and writing 1 has

no effect.

Bits 6:5 Reserved, must be kept at reset value.

Bit 4 DIR: Direction of transaction

This bit is written by the hardware according to the direction of the successful transaction,

which generated the interrupt request.

If DIR bit = 0, VTTX bit is set in the USB_CHEPnR register related to the interrupting

endpoint. The interrupting transaction is of IN type (data transmitted by the USB peripheral to

the host PC).

If DIR bit = 1, VTRX bit or both VTTX/VTRX are set in the USB_CHEPnR register related to

the interrupting endpoint. The interrupting transaction is of OUT type (data received by the

USB peripheral from the host PC) or two pending transactions are waiting to be processed.

This information can be used by the application software to access the USB_CHEPnR bits

related to the triggering transaction since it represents the direction having the interrupt

pending. This bit is read-only.

Bits 3:0 IDN[3:0]: Device Endpoint / host channel identification number

These bits are written by the hardware according to the host channel or device endpoint

number, which generated the interrupt request. If several endpoint/channel transactions are

pending, the hardware writes the identification number related to the endpoint/channel

having the highest priority defined in the following way: two levels are defined, in order of

priority: isochronous and double-buffered bulk channels/endpoints are considered first and

then the others are examined. If more than one endpoint/channel from the same set is

requesting an interrupt, the IDN bits in USB_ISTR register are assigned according to the

lowest requesting register, CHEP0R having the highest priority followed by CHEP1R and so

on. The application software can assign a register to each endpoint/channel according to this

priority scheme, so as to order the concurring endpoint/channel requests in a suitable way.

These bits are read only.

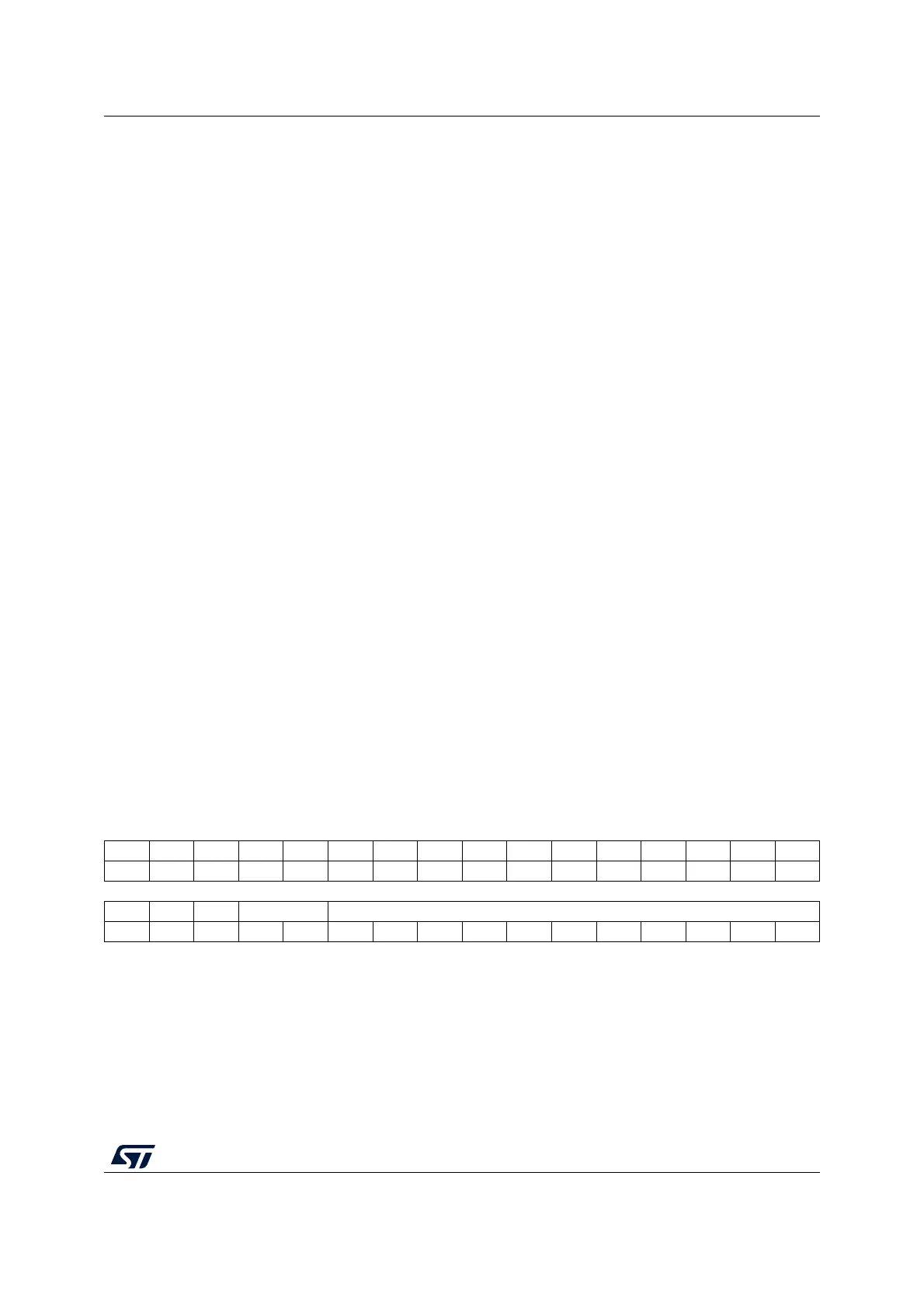

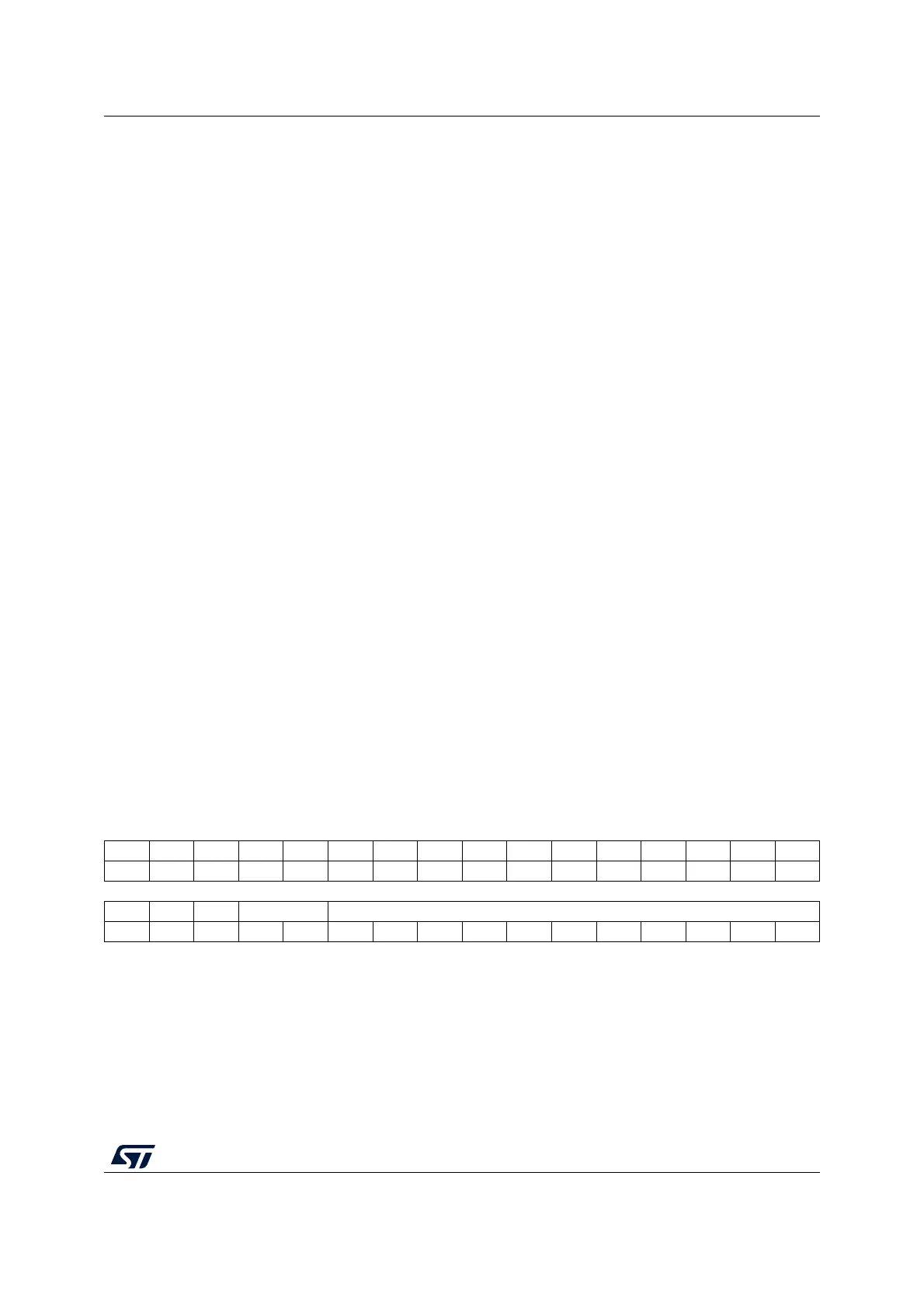

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

RXDP RXDM LCK LSOF[1:0] FN[10:0]

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 RXDP: Receive data + line status

This bit can be used to observe the status of received data plus upstream port data line. It

can be used during end-of-suspend routines to help determining the wakeup event.

Bit 14 RXDM: Receive data - line status

This bit can be used to observe the status of received data minus upstream port data line. It

can be used during end-of-suspend routines to help determining the wakeup event.

Loading...

Loading...