Universal serial bus full-speed host/device interface (USB) RM0444

1290/1390 RM0444 Rev 5

USB Device address (USB_DADDR)

Address offset: 0x4C

Reset value: 0x0000 0000

Bit 13 LCK: Locked

– Device mode

This bit is set by the hardware when at least two consecutive SOF packets have been

received after the end of an USB reset condition or after the end of an USB resume

sequence. Once locked, the frame timer remains in this state until an USB reset or USB

suspend event occurs.

Bits 12:11 LSOF[1:0]: Lost SOF

– Device mode

These bits are written by the hardware when an ESOF interrupt is generated, counting the

number of consecutive SOF packets lost. At the reception of an SOF packet, these bits are

cleared.

Bits 10:0 FN[10:0]: Frame number

This bit field contains the 11-bits frame number contained in the last received SOF packet.

The frame number is incremented for every frame sent by the host and it is useful for

isochronous transfers. This bit field is updated on the generation of an SOF interrupt.

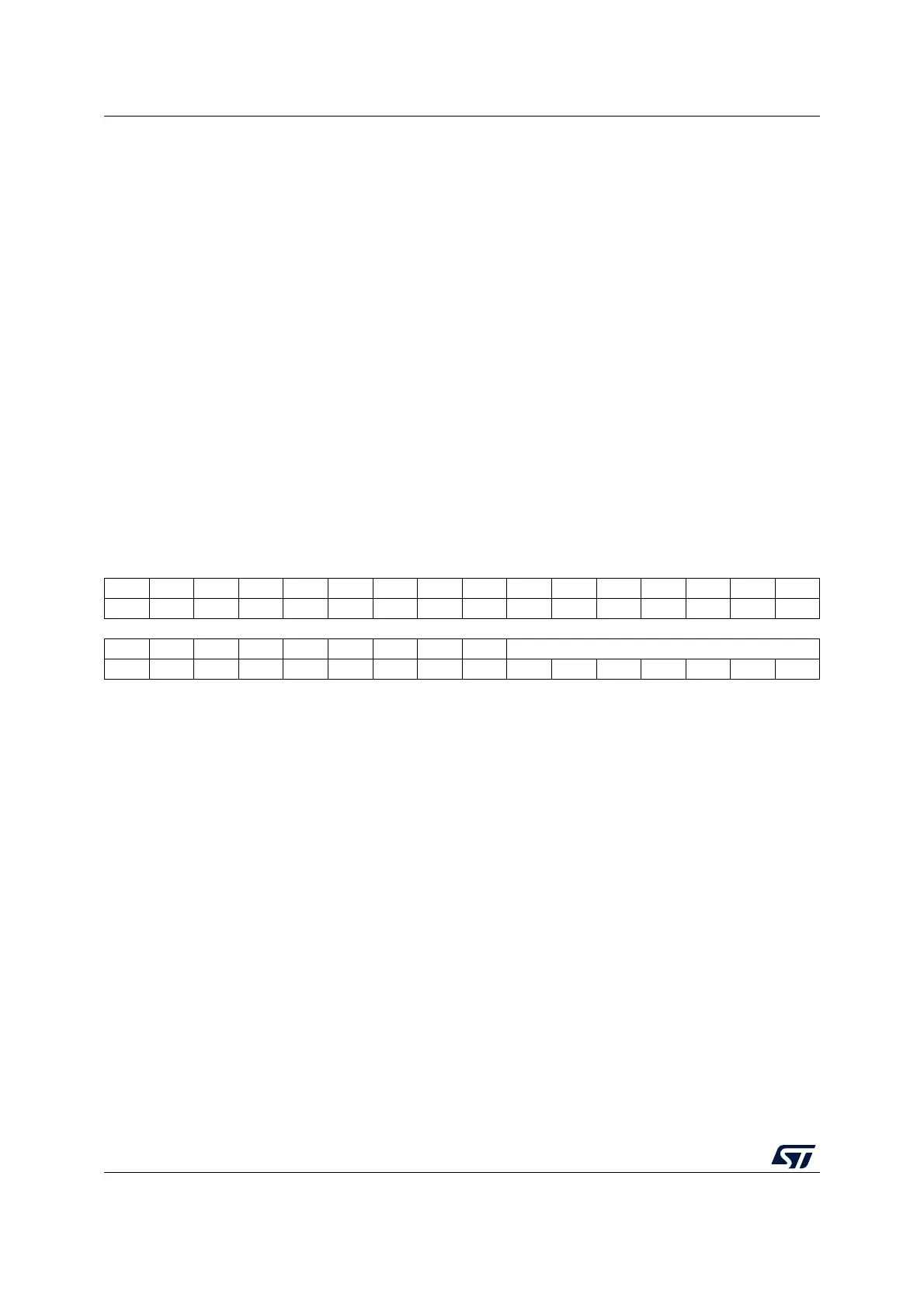

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. EF ADD[6:0]

rw rw rw rw rw rw rw rw

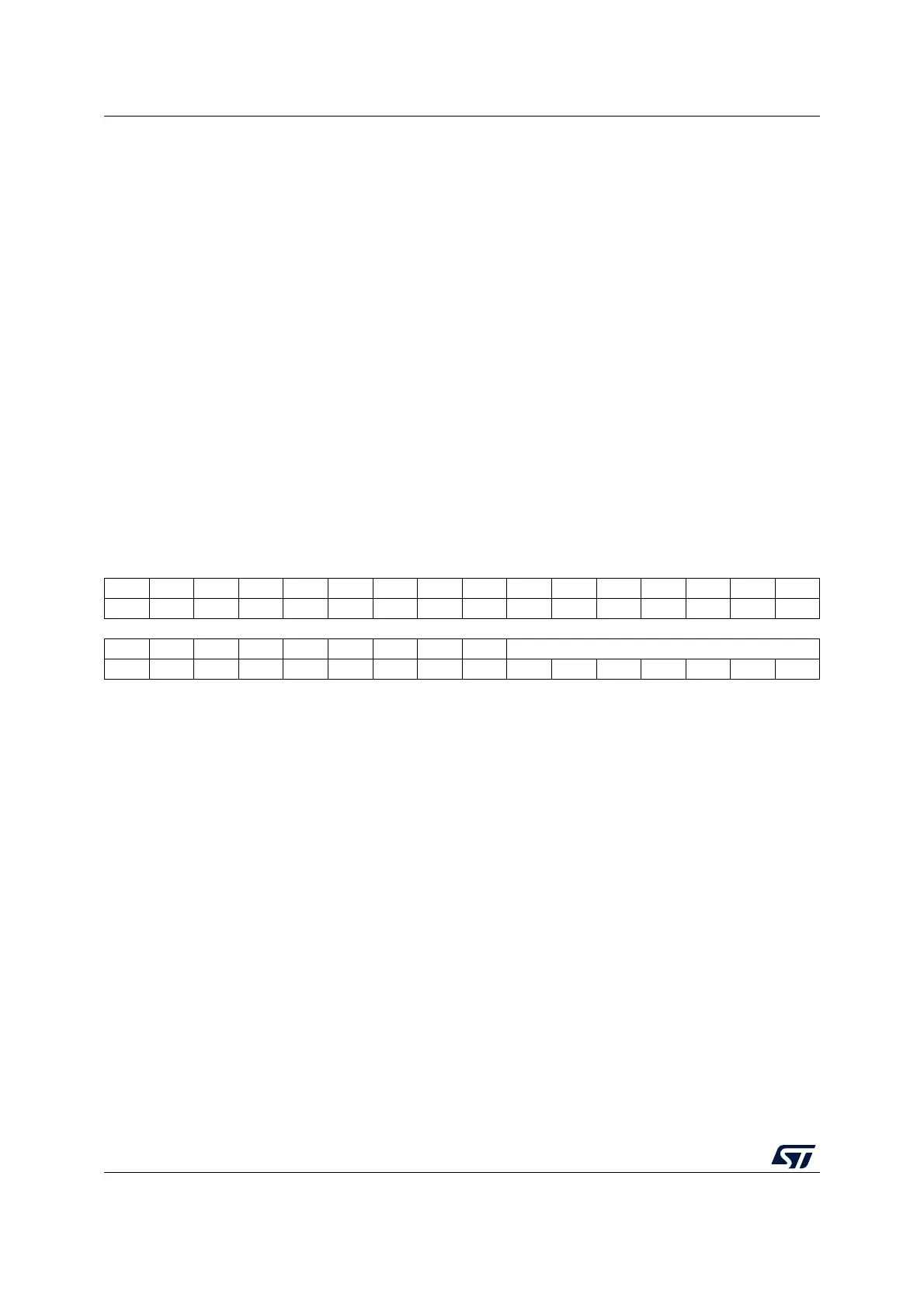

Bits 31:8 Reserved, must be kept at reset value.

Bit 7 EF: Enable function

This bit is set by the software to enable the USB Device. The address of this device is

contained in the following ADD[6:0] bits. If this bit is at 0 no transactions are handled,

irrespective of the settings of USB_CHEPnR registers.

Bits 6:0 ADD[6:0]: Device address

– Device mode

These bits contain the USB function address assigned by the host PC during the

enumeration process. Both this field and the endpoint/channel address (EA) field in the

associated USB_CHEPnR register must match with the information contained in a USB

token in order to handle a transaction to the required endpoint.

– Host mode

These bits contain the address transmitted with the LPM transaction

Loading...

Loading...