RM0444 Rev 5 181/1390

RM0444 Reset and clock control (RCC)

220

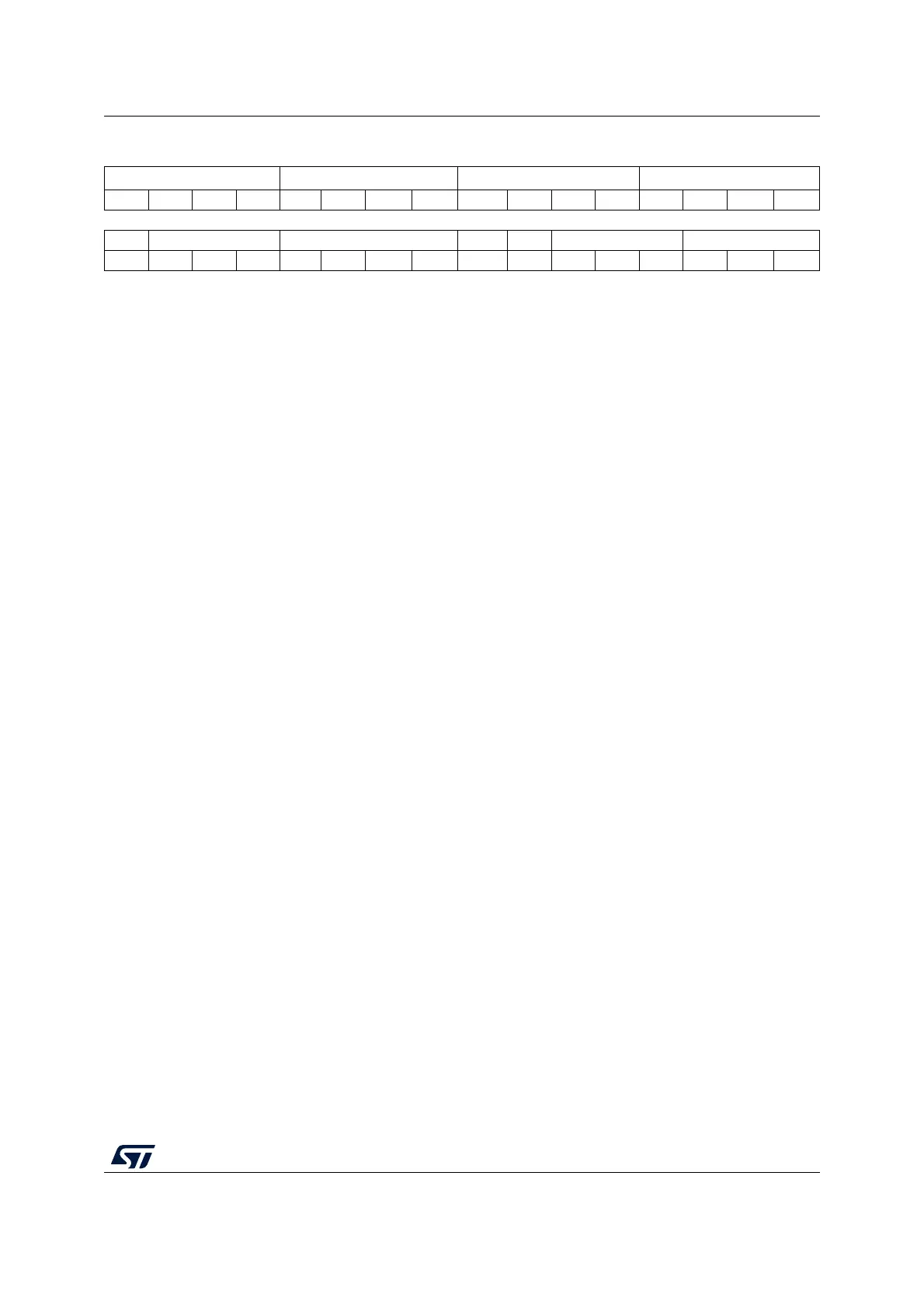

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

MCOPRE[3:0] MCOSEL[3:0]

MCO2PRE[3:0]

(1)

MCO2SEL[3:0]

(1)

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

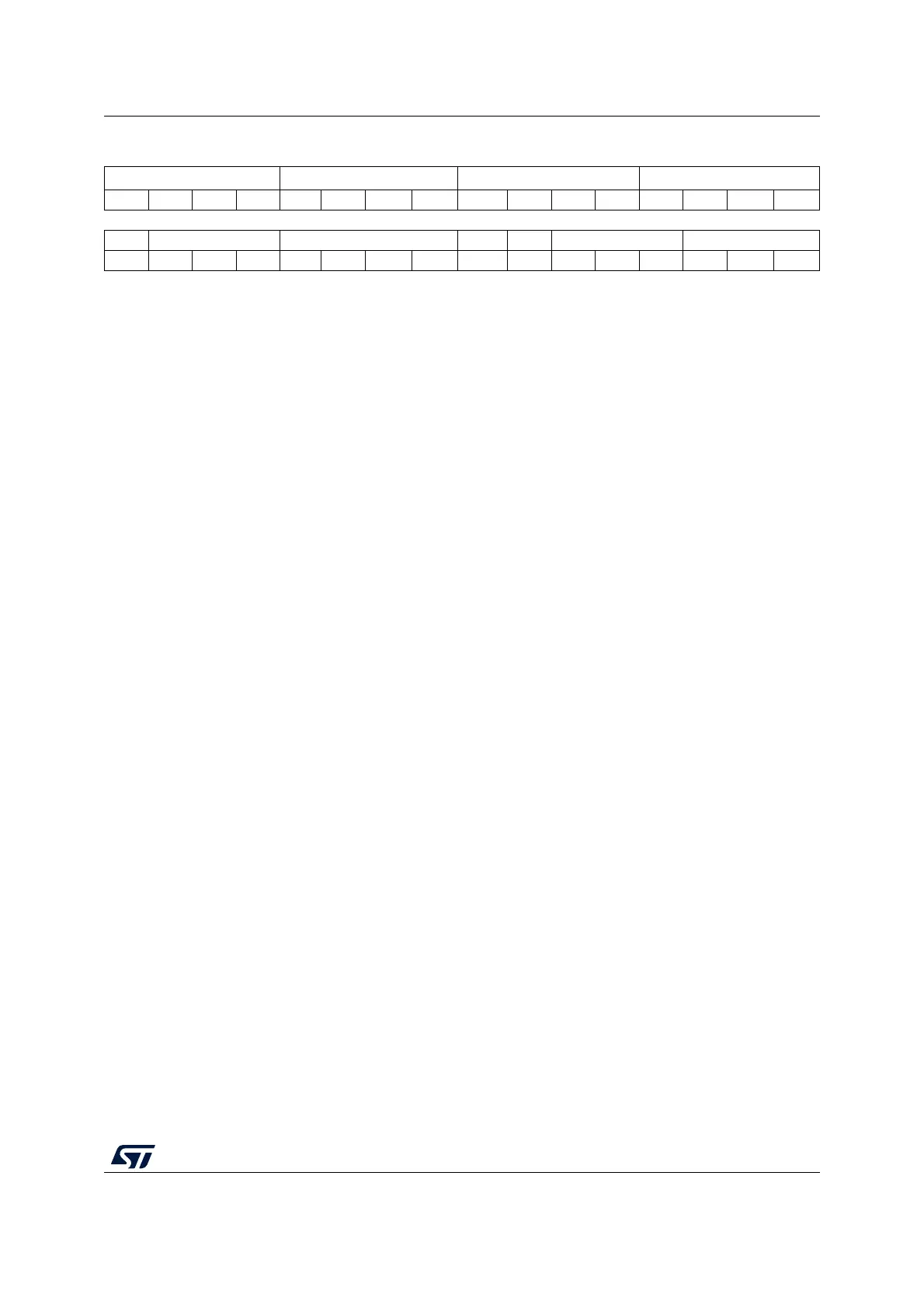

1514131211109 8 7 654321 0

Res. PPRE[2:0] HPRE[3:0] Res. Res. SWS[2:0] SW[2:0]

rw rw rw rw rw rw rw r r r rw rw rw

1. Only significant on devices integrating the corresponding output, otherwise reserved. Refer to Section 1.4: Availability of

peripherals.

Bits 31:28 MCOPRE[3:0]: Microcontroller clock output prescaler

This bitfield is controlled by software. It sets the division factor of the clock sent to the MCO

output as follows:

0000: 1

0001: 2

0010: 4

...

0111: 128

1000: 256

1001: 512

1010: 1024

Other: reserved

It is highly recommended to set this field before the MCO output is enabled.

Note: Values above 0111 are only significant for STM32G0B1xx and STM32G0C1xx.

Reserved for the other devices.

Bits 27:24 MCOSEL[3:0]: Microcontroller clock output clock selector

This bitfield is controlled by software. It sets the clock selector for MCO output as follows:

0000: no clock, MCO output disabled

0001: SYSCLK

0010: HSI48

0011: HSI16

0100: HSE

0101: PLLRCLK

0110: LSI

0111: LSE

1000: PLLPCLK

1001: PLLQCLK

1010: RTCCLK

1011: RTC WAKEUP

Note: This clock output may have some truncated cycles at startup or during MCO clock

source switching.

Values above 0111 and the value 0010 are only significant for STM32G0B1xx and

STM32G0C1xx. Reserved for the other devices.

Loading...

Loading...