Embedded Flash memory (FLASH) RM0444

86/1390 RM0444 Rev 5

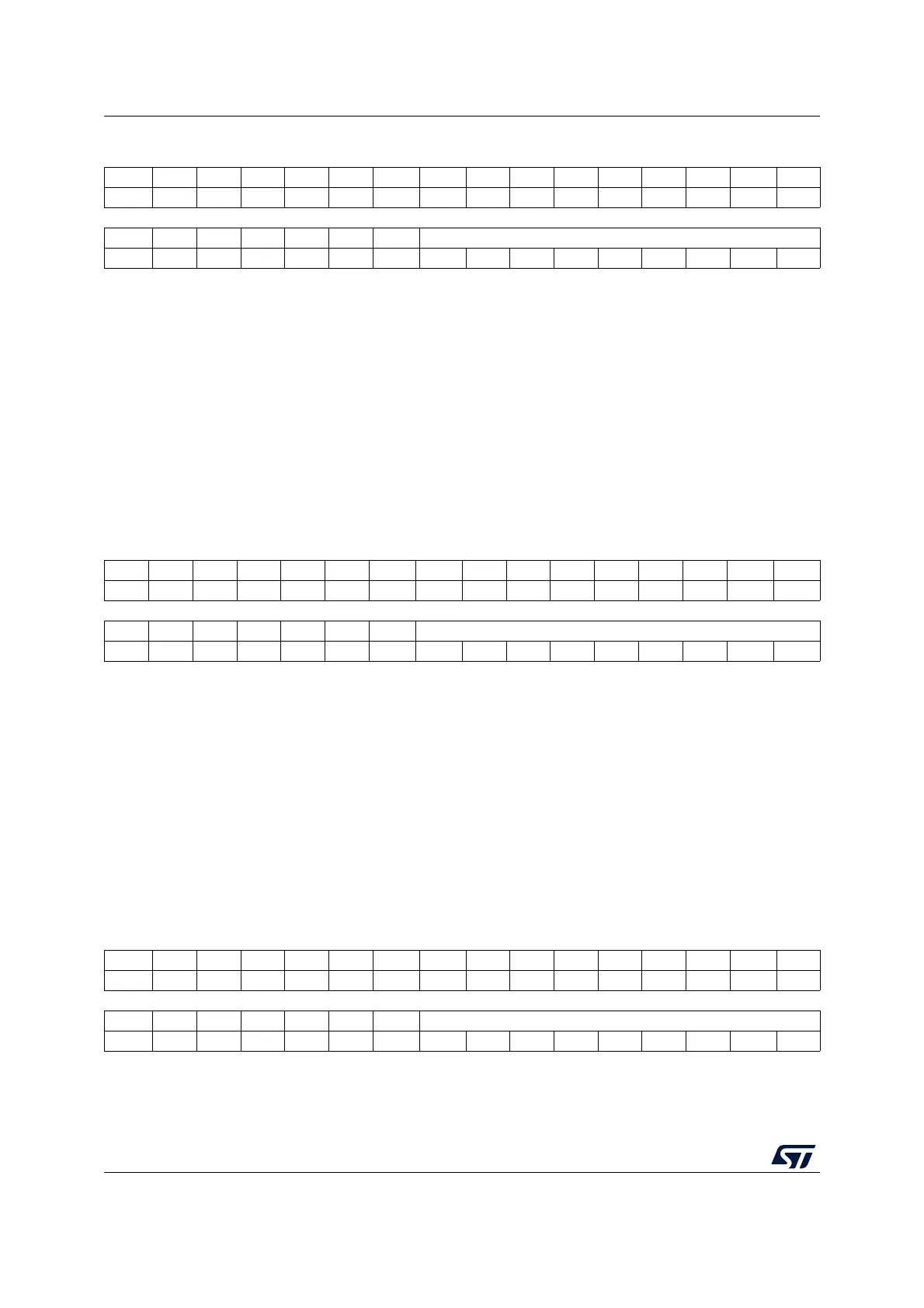

PCROP2A start address option bytes

Flash memory address: 0x1FFF 7838

Reset value: 0xFFFF FFFF (ST production value)

The register pertains to dual-bank devices only. In single-bank devices, it is reserved.

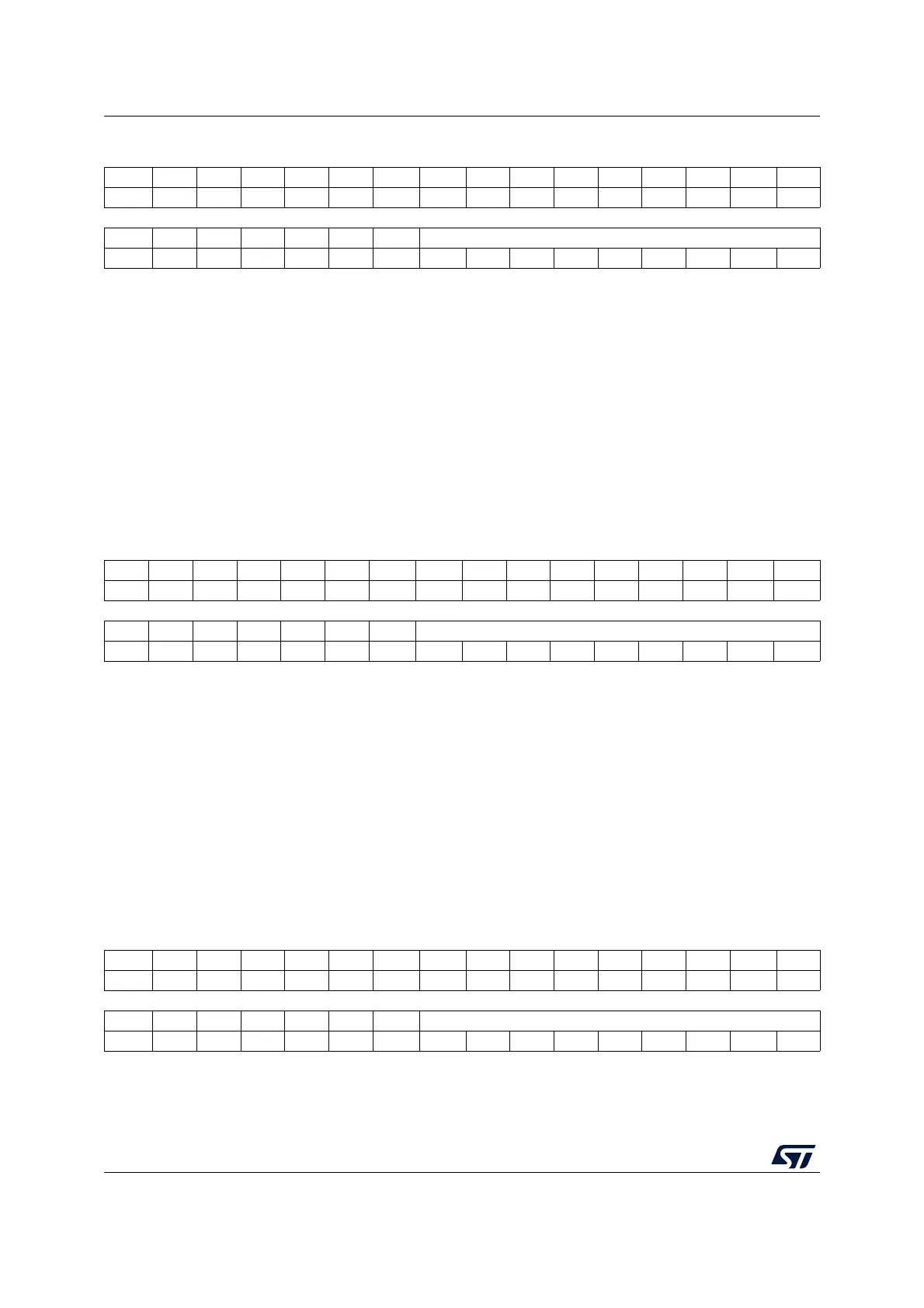

PCROP2A end address option bytes

Flash memory address: 0x1FFF 7840

Reset value: 0x0000 0000 (ST production value)

The register pertains to dual-bank devices only. In single-bank devices, it is reserved.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. PCROP1B_END[8:0]

r rrrrrr rr

Bits 31:9 Reserved, must be kept at reset value.

Bits 8:0 PCROP1B_END[8:0]: PCROP1B area end offset (Bank 1)

PCROP1B_END contains the offset of the last PCROP subpage of the PCROP1B area (in

Bank 1 for dual-bank devices).

Note: Values corresponding to addresses outside the Main memory are not allowed.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res. Res. Res. PCROP2A_STRT[8:0]

r rrrrrrr r

Bits 31:9 Reserved, must be kept at reset value.

Bits 8:0 PCROP2A_STRT[8:0]: PCROP2A area start offset, Bank 2

PCROP2A_STRT contains the offset of the first PCROP subpage of the PCROP2A area in

Bank 2 of dual-bank devices.

Note: Values corresponding to addresses outside the Main memory are not allowed.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. PCROP2A_END[8:0]

r rrrrrr rr

Loading...

Loading...