Reset and clock control (RCC) RM0351

240/1693 DocID024597 Rev 3

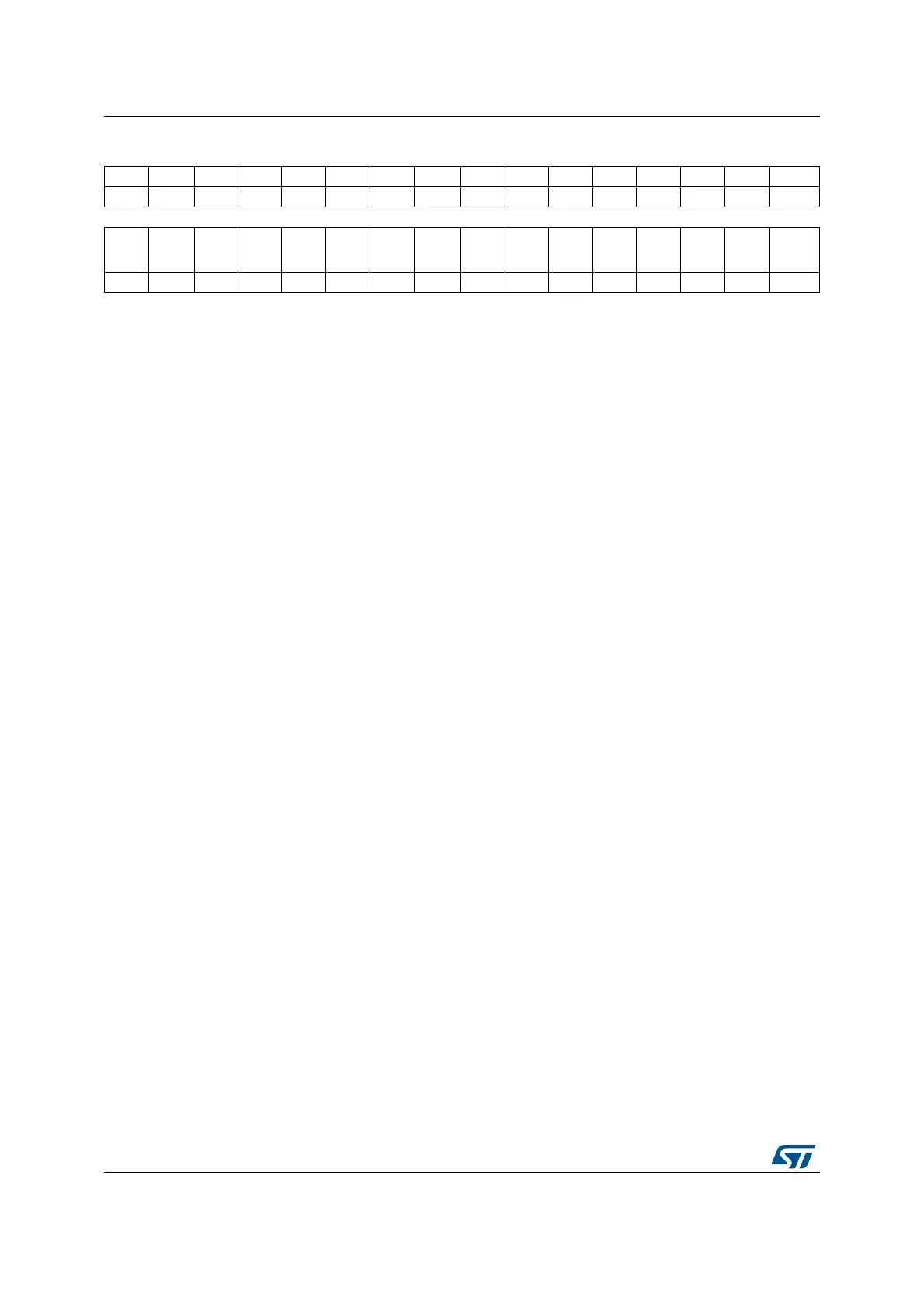

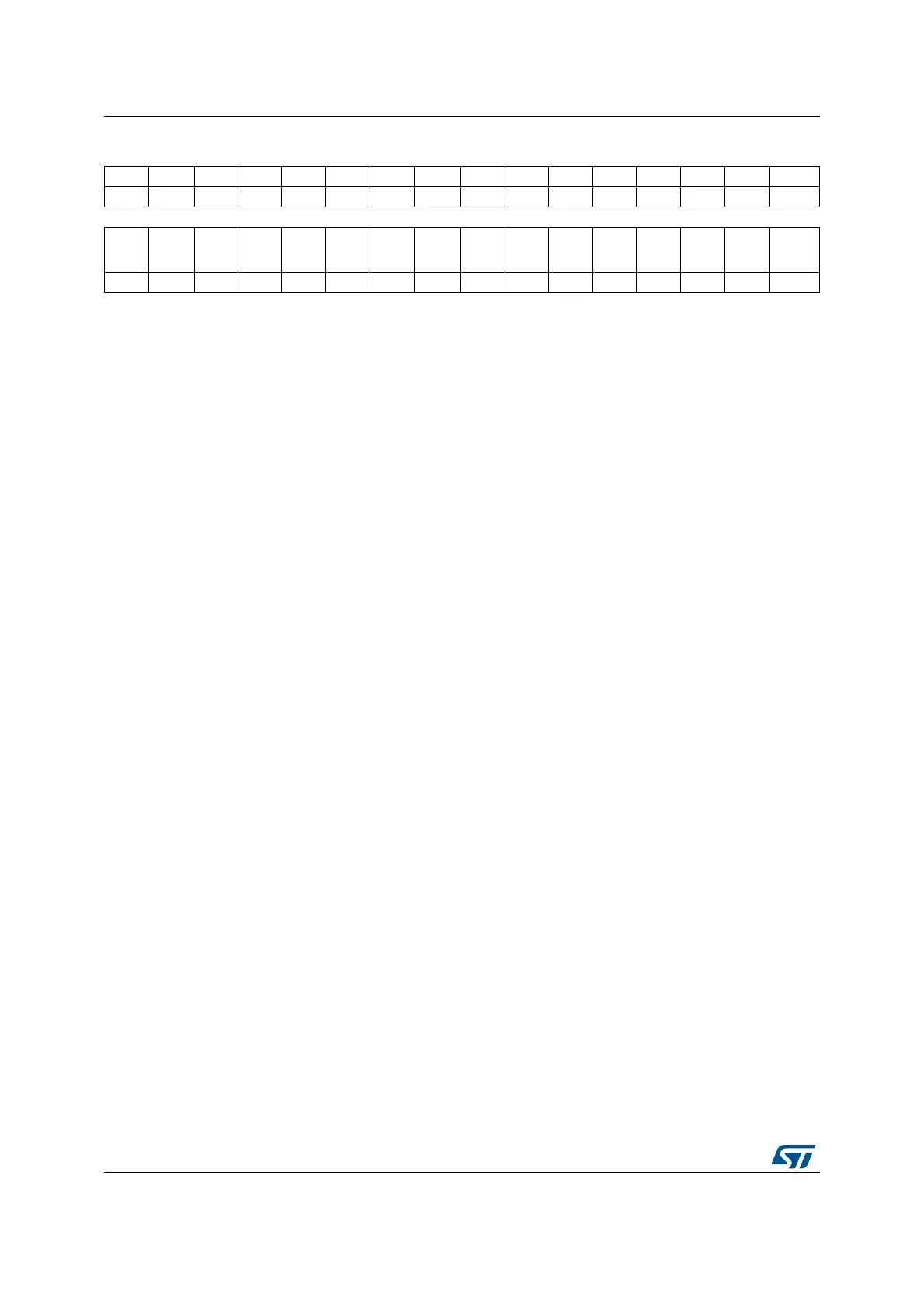

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109 8 7654321 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

LPTIM

2SMEN

Res. Res.

SWP

MI1

SMEN

Res.

LP

UART1

SMEN

rw rw rw

Bits 31:6 Reserved, must be kept at reset value.

Bit 5 LPTIM2SMEN Low power timer 2 clocks enable during Sleep and Stop modes

Set and cleared by software.

0: LPTIM2 clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: LPTIM2 clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bits 4:3 Reserved, must be kept at reset value.

Bit 2 SWPMI1SMEN: Single wire protocol clocks enable during Sleep and Stop modes

Set and cleared by software.

0: SWPMI1 clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: SWPMI1 clocks enabled by the clock gating

(1)

during Sleep and Stop modes

Bit 1 Reserved, must be kept at reset value.

Bit 0 LPUART1SMEN: Low power UART 1 clocks enable during Sleep and Stop modes

Set and cleared by software.

0: LPUART1 clocks disabled by the clock gating

(1)

during Sleep and Stop modes

1: LPUART1 clocks enabled by the clock gating

(1)

during Sleep and Stop modes

1. This register only configures the clock gating, not the clock source itself. Most of the peripherals are clocked by a single

clock (AHB or APB clock), which is always disabled in Stop mode. In this case setting the bit has no effect in Stop mode.

Loading...

Loading...