e200z6 Core Complex

MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 3-17

• UX—User execute permission. Allows instruction fetches to access the page and instructions to be

executed from the page while in user mode.

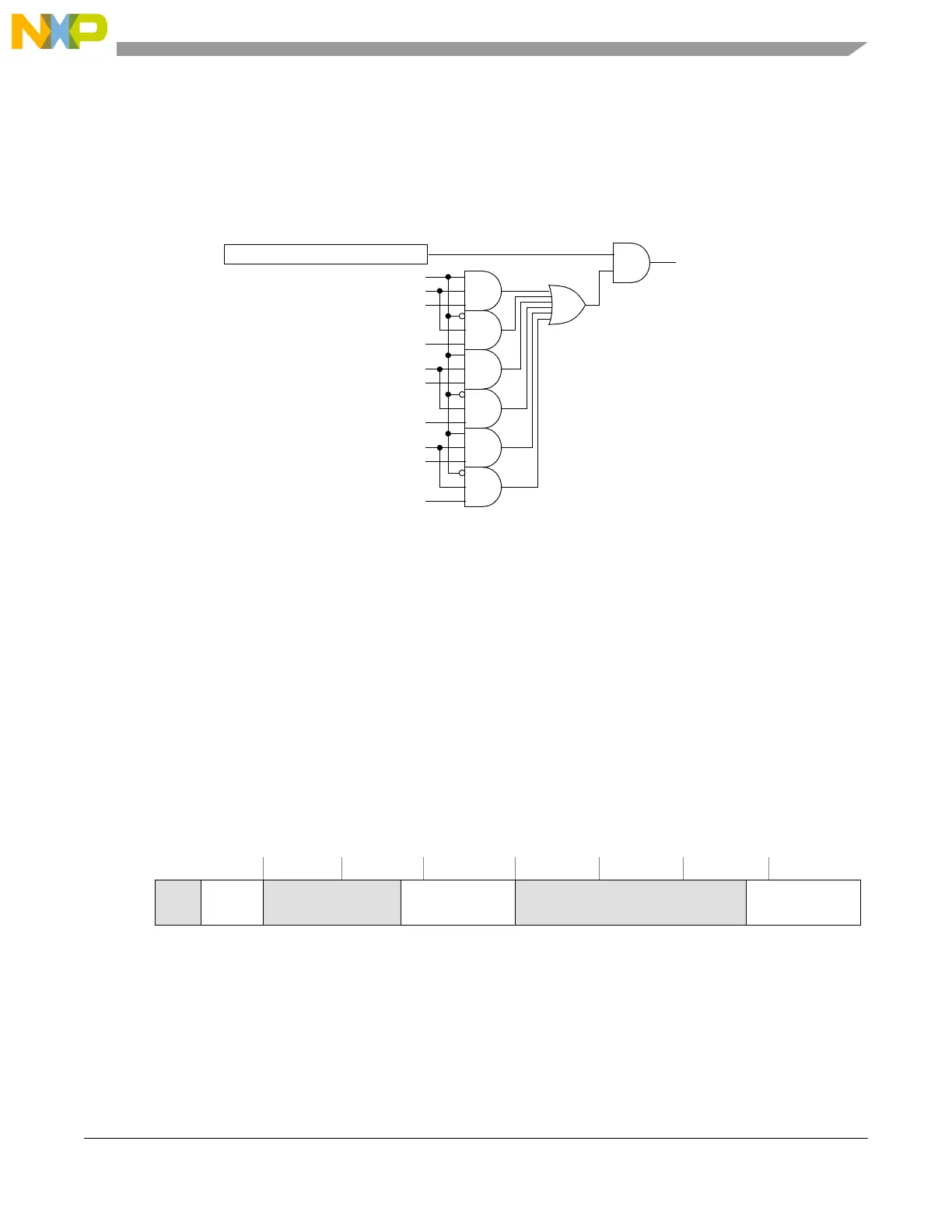

If the translation match was successful, the permission bits are checked as shown in Figure 3-6. If the

access is not allowed by the access permission mechanism, the processor generates an instruction or data

storage interrupt (ISI or DSI).

Figure 3-6. Granting of Access Permission

3.3.1.5 MMU Assist Registers (MAS[0:4], MAS[6])

The e200z6 uses six special purpose registers (MAS[0], MAS[1], MAS[2], MAS[3], MAS[4], and

MAS[6]) to facilitate reading, writing, and searching the TLBs. The MAS registers can be read or written

using the mfspr and mtspr instructions. The e200z6 does not implement the MAS5 register, present in

other Freescale EIS designs, because the tlbsx instruction only searches based on a single SPID value.

For more information on the MASn registers is available in the e200z6 PowerPC

TM

Core Reference

Manual.

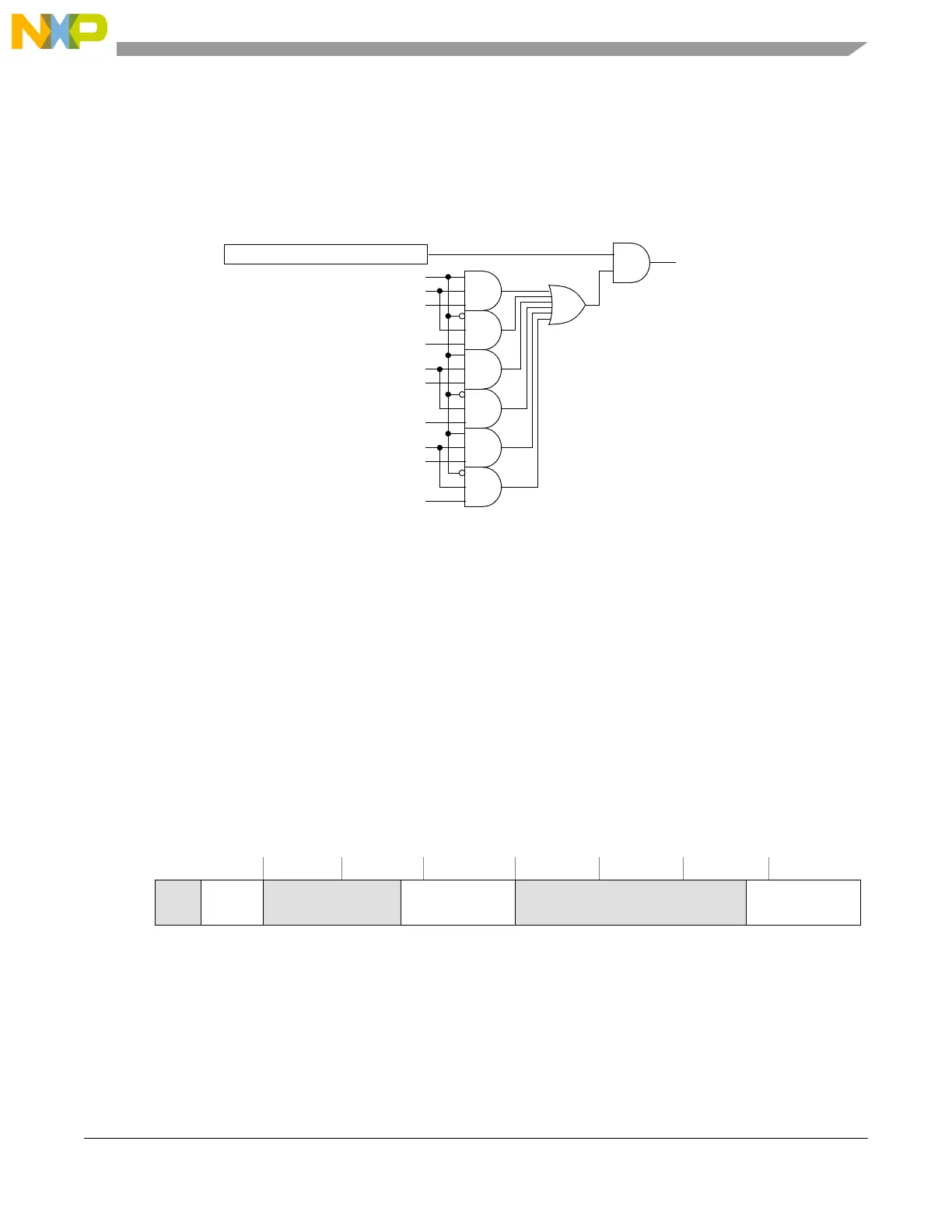

3.3.1.5.1 MAS[0] Register

The MAS[0] register is shown in Figure 3-7.

MAS[0] fields are defined in Table 3-3.

SPR: 624 Access: R/W

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

— TLBSEL — ESEL —NV

W

Reset Undefined on Power Up ⎯ Unchanged on Reset

Figure 3-7. MAS Register 0 Format — MAS[0]

Access Granted

Instruction Fetch

MSR[PR]

TLB_entry[UX]

TLB_entry[SX]

Load-class Data Access

TLB_entry[UR]

TLB_entry[SR]

Store-class Data Access

TLB_entry[UW]

TLB_entry[SW]

TLB

Loading...

Loading...