MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 10-1

Chapter 10

Interrupt Controller (INTC)

10.1 Introduction

This chapter describes the interrupt controller (INTC), which schedules interrupt requests (IRQs) from

software and internal peripherals to the e200z6 core. The INTC provides interrupt prioritization and

preemption, interrupt masking, interrupt priority elevation, and protocol support.

Interrupts implemented by the MCU are defined in the e200z6 PowerPC

tm

Core Reference Manual.

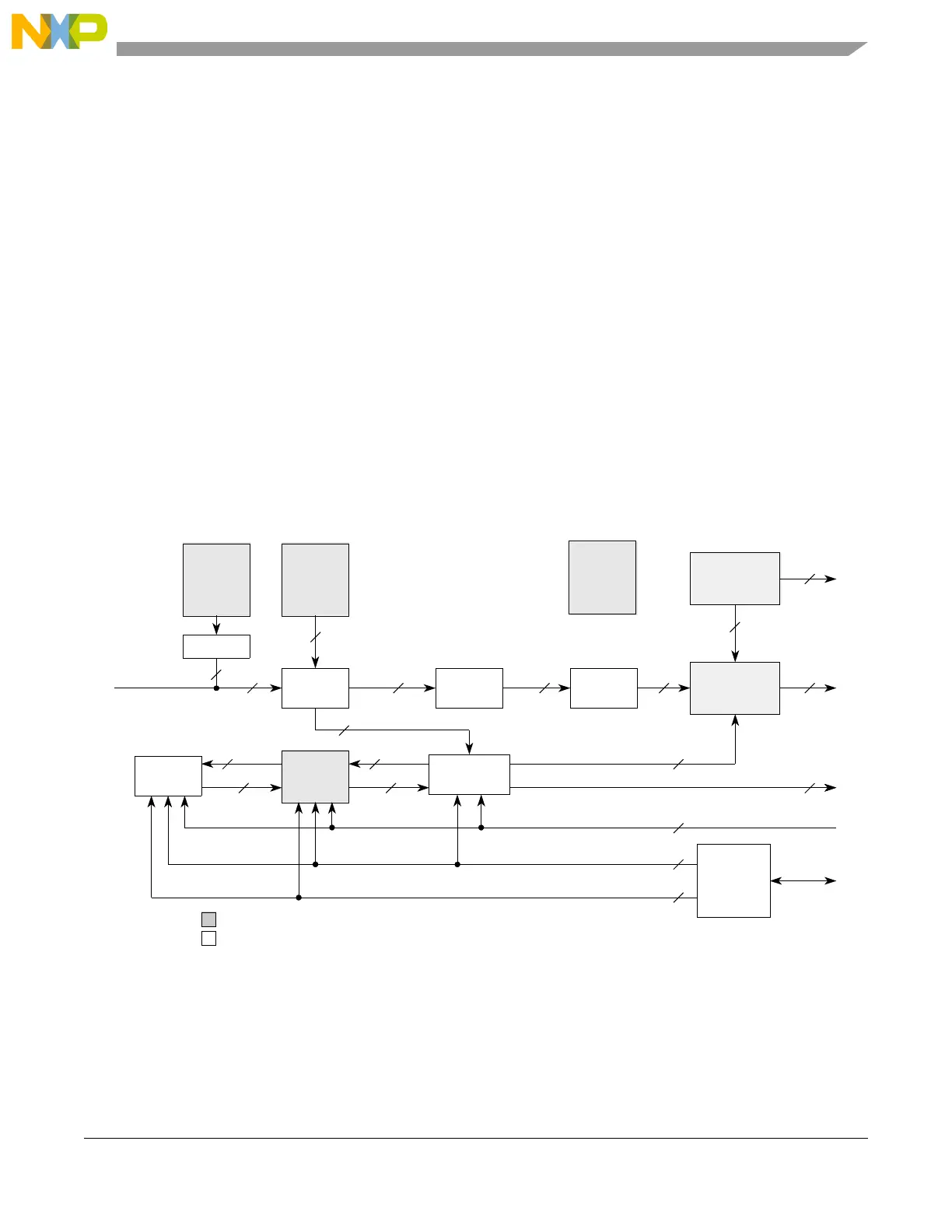

10.1.1 Block Diagram

Figure 4-1 shows details of the interrupt controller.

Figure 10-1. INTC Block Diagram

End-of-

interrupt

register

Software

set clear

interrupt

registers

Flag bits

Priority

select

registers

8

Peripheral

interrupt

requests

1

n

1

Priority

arbitrator

n

1

Highest

priority

interrupt

requests

n

1

Request

selector

Lowest

vector

interrupt

request

n

1

Vector

encoder

Interrupt

vector

9

x 4-bits

Interrupt

acknowledge

register

Interrupt

vector

9

Hardware

vector

enable

Vector table

entry size

1

Module

configuration

register

1

Highest priority

4

Priority

comparator

New

4

Current

4

priority

Current

priority

register

priority

4

Popped

4

priority

Pushed

priority

Priority

LIFO

Slave

interface

for reads

and writes

1

Push/update/acknowledge

1

Pop

Slave

bus

signals

1

Interrupt acknowledge

1

Update interrupt vector

1

Interrupt

request to

processor

Memory-mapped registers

Logic not memory-mapped

1

Although N (largest addressable IRQ vector number) = 329, this does not indicate the total number of interrupts

available on this device. The total number of available interrupts on this device is 332: 298 peripheral IRQs, eight

software-configurable IRQs, and 16 reserved.

Loading...

Loading...