SRAM

MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 14-3

3. The ECC is then calculated on the resulting 64 bits formed in the previous step.

4. The 8-bit ECC result is appended to the 64 bits from the data bus, and the 72-bit value is then

written to SRAM.

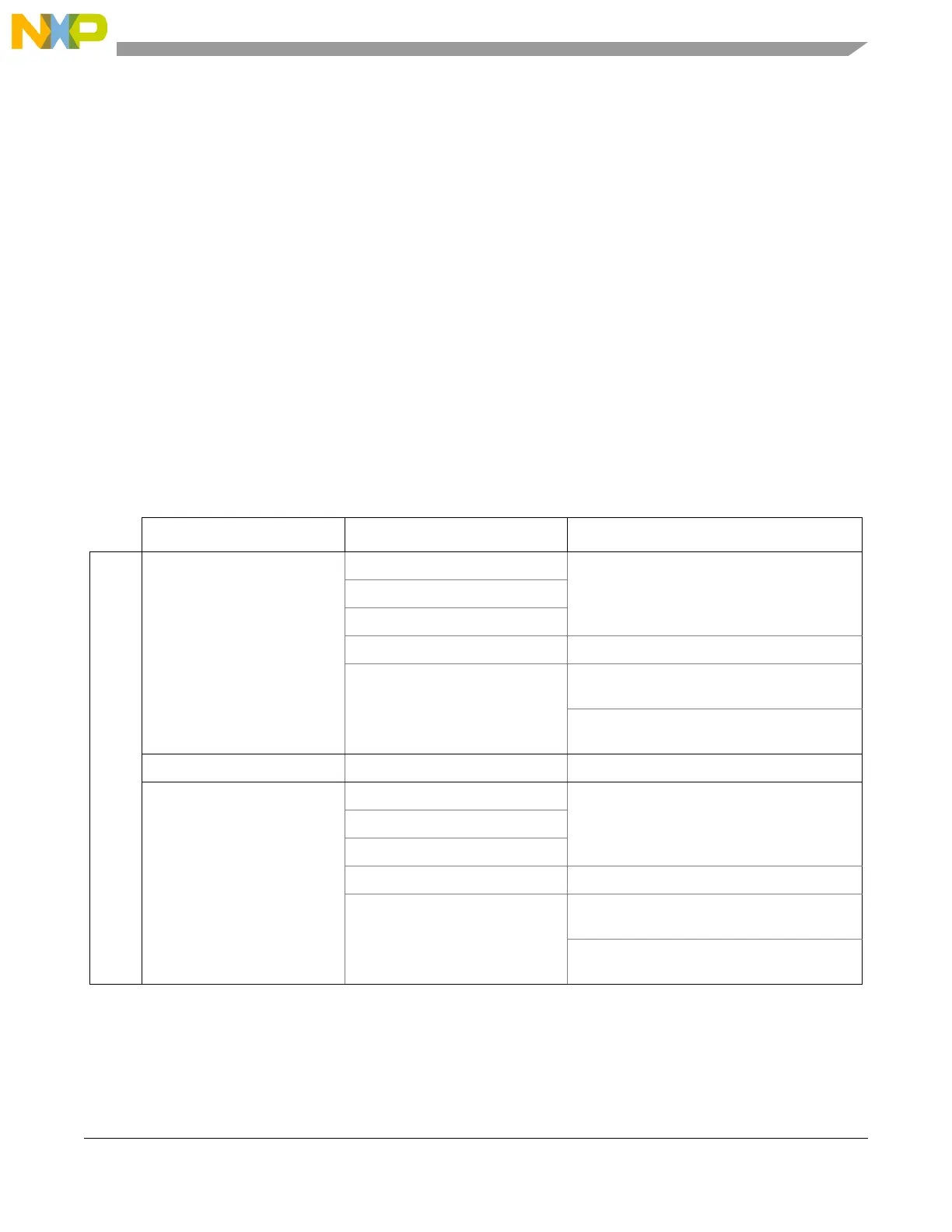

14.6.1 Access Timing

The system bus is a two-stage pipelined bus, which makes the timing of any access dependent on the access

during the previous clock. Table 14-3 lists the various combinations of read and write operations to SRAM

and the number of wait states used for the each operation. The table columns contain the following

information:

Current operation Lists the type of SRAM operation executing currently

Previous operation Lists the valid types of SRAM operations that can precede the current SRAM

operation (valid operation during the preceding clock)

Wait states Lists the number of wait states (bus clocks) the operation requires which depends

on the combination of the current and previous operation

Table 14-3. Number of Wait States Required for SRAM Operations

Current Operation Previous Operation Number of Wait States Required

Read Operation

Read

Idle

1Pipelined read

Burst read

64-bit write 2

8-, 16-, or 32-bit write

0

(read from the same address)

1

(read from a different address)

Pipelined read Read 0

Burst read

Idle

1,0,0,0Pipelined read

Burst read

64-bit write 2,0,0,0

8-, 16-, or 32-bit write

0,0,0,0

(read from the same address)

1,0,0,0

(read from a different address)

Loading...

Loading...