External Bus Interface (EBI)

MPC5566 Microcontroller Reference Manual, Rev. 2

12-56 Freescale Semiconductor

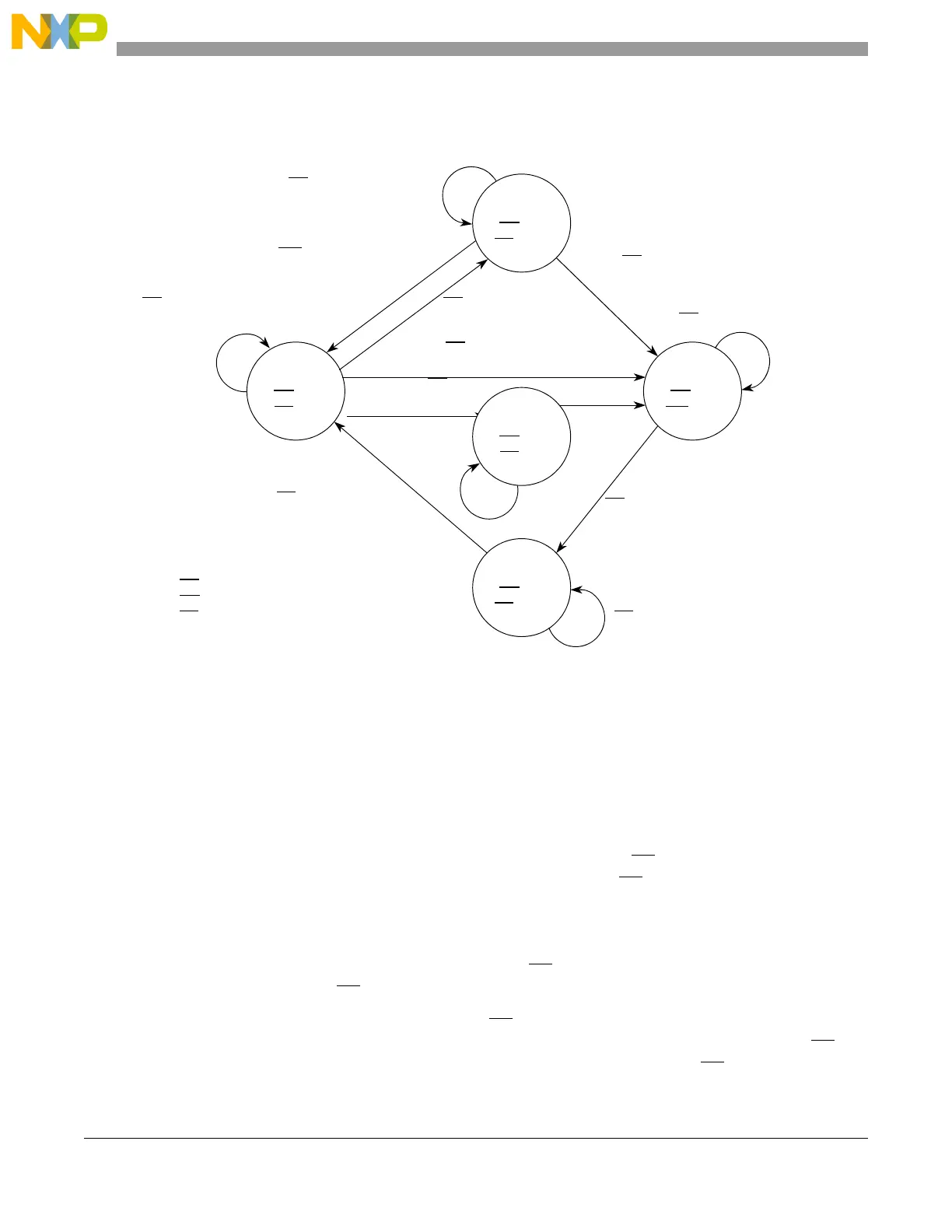

Figure 12-36 shows the internal finite state machine that implements the arbiter protocol.

Figure 12-36. Internal Bus Arbitration State Machine

12.4.2.9 Termination Signals Protocol

The termination signals protocol was defined to avoid electrical contention on lines that can be driven by

various sources. To do that, a slave must not drive signals associated with the data transfer until the address

phase is completed and it recognizes the address as its own. The slave must disconnect from signals

immediately after it acknowledges the cycle and not later than the termination of the next address phase

cycle.

For EBI-mastered non-chip select accesses, the EBI requires assertion of TA from an external device to

signal that the bus cycle is complete. The EBI uses a latched version of TA

(delayed one cycle) for these

accesses to help make timing at high frequencies. This results in the EBI driving the address and control

signals one cycle longer than required, as seen in Figure 12-37. However, the DATA does not need to be

held one cycle longer by the slave, because the EBI latches DATA every cycle during non-chip select

accesses. During these accesses, the EBI does not drive the TA

signal, leaving it up to an external device

(or weak internal pullup) to drive TA.

For EBI-mastered chip select accesses, the EBI drives TA the entire cycle, asserting according to internal

wait state counters to terminate the cycle. During idle periods on the external bus, the EBI drives TA

negated as long as it is granted the bus; when it no longer owns the bus it lets go of TA

. When an external

External

IRP = 1 and

BB

= 1 and RBG = 0

BB = 0 or RBG = 1

ETP = 1 and BR = 0 and

Owner

BG

= 0

BB

= hiZ

(IRP = 0 or EHP = 1)

MCU

Bus Wait

BG

= 1

BB

= hiZ

(BR

= 1 or EHP = 0)

ETP = 0

BR = 0 and ETP = 0 and

(IRP = 0 or EHP = 1)

External

Bus Wait

BG

= 0

BB = 0

MCU

Owner Busy

BG

= 1

BB

= 0

MCU

Owner Idle

BG = 1

BB = hiZ

ETP = 0 and ((BR = 0 and IRP = 0)

or (BR

= 0 and EHP = 1) or

(IRP = 0 and EHP = 1))

IRP = 0 or

(BR

= 0 and EHP = 1)

BR

= 1 and ETP = 0

and IRP = 0

((BR = 1 or EHP = 0)

and IRP = 1) or ETP = 1

(BR = 1 and (ETP = 1 or IRP = 1))

or (IRP = 1 and EHP = 0)

BR = 1 and IRP = 0 and

ETP = 0 and EHP = 0

ETP = 1

ETP = External Transaction in Progress

IRP = Internal Request Pending

EHP = External has Higher Priority

BR

= Bus Request

BG = Bus Grant

BB

= Bus Busy

Loading...

Loading...