e200z6 Core Complex

MPC5566 Microcontroller Reference Manual, Rev. 2

3-30 Freescale Semiconductor

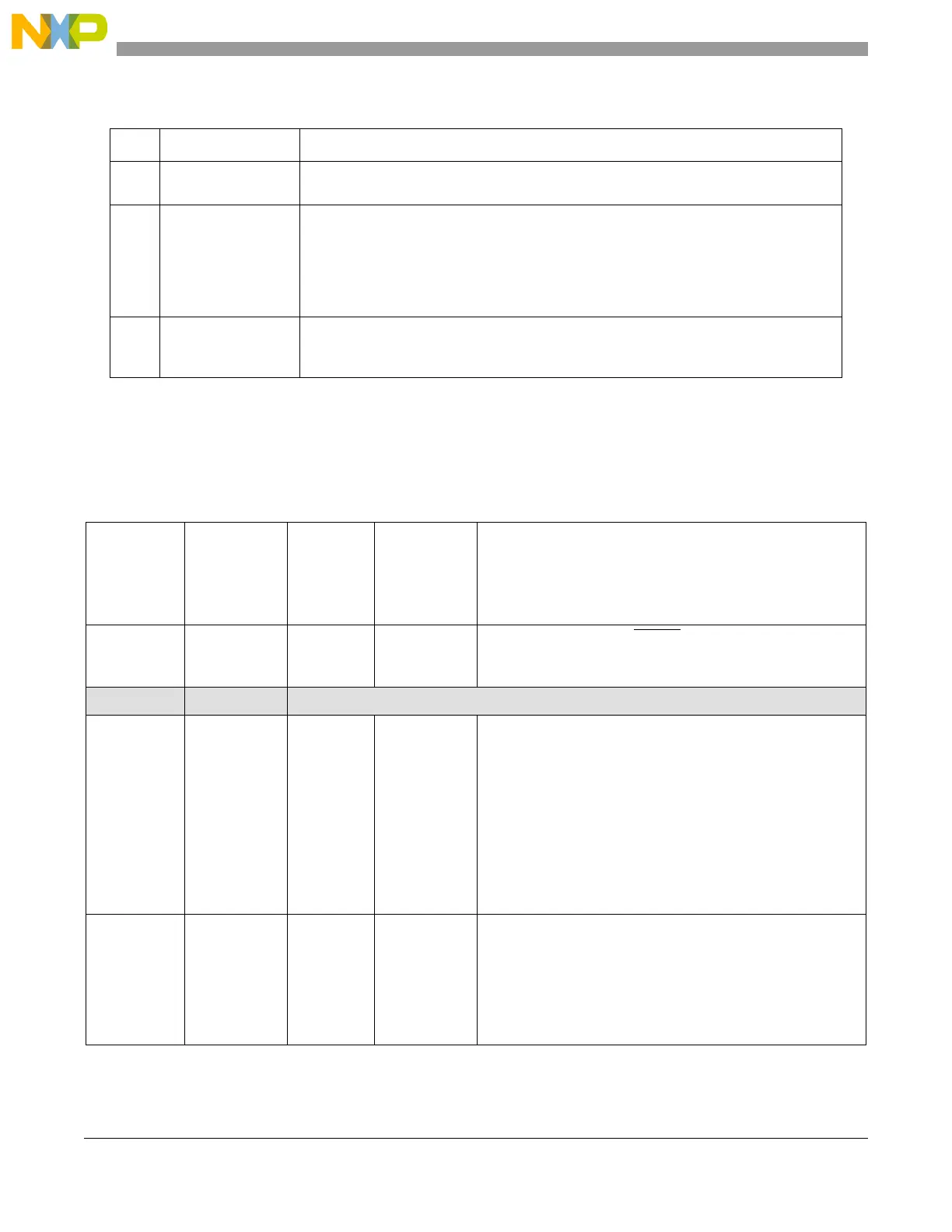

3.3.3 Interrupt Types

The interrupts implemented in the device and the exception conditions that cause them are listed in

Table 3-11.

12 CPA

Cache parity available

1 - The cache implements parity

13:20 CNWAY

Number of ways in the data cache

0x03 - The cache is 4-way set-associative

0x07 - The cache is 8-way set-associative

Note: CNWAY shows the current cache organization as set by L1CSR0[CORG].

21:31 CSIZE

Cache size

0x020 - The size of the cache is 32 KB

Table 3-11. Interrupts and Conditions

Interrupt

Type

Interrupt

Vector Offset

Register

Enables

1

Core Register

in Which

State

Information is

Saved

Causing Conditions

System reset none,

vector to

0xFFFF_FFFC

• Reset by assertion of RESET

• Watchdog timer reset control

• Debug reset control

Critical input IVOR 0 IVOR 0 is not supported in the device

Machine

check

IVOR 1 ME CSSR[0:1] Machine check conditions:

• Machine check exception (p_mcp_b) asserts

and MSR[ME] = 1.

• ISI, ITLB error occurred on: the first instruction fetch for the

exception handler, and the current MSR[ME] = 1.

• Parity error detected on the cache access and the current

MSR[ME] = 1.

• Write bus error occurred on: a buffered store or cache-line

push; and the current MSR[ME] = 1.

• Bus error (XTE) with MSR[EE] = 0 and current

MSR[ME] = 1.

Data storage IVOR 2 — SRR[0:1] Data storage conditions:

• Access control

• Byte ordering error from a misaligned access across a page

boundary to a page with mismatched E bits

• Cache locking exception

• Precise external termination error and the current

MSR[ME] = 1.

Table 3-10. L1CFG0 Field Descriptions (continued)

Bits Name Description

Loading...

Loading...