External Bus Interface (EBI)

MPC5566 Microcontroller Reference Manual, Rev. 2

12-66 Freescale Semiconductor

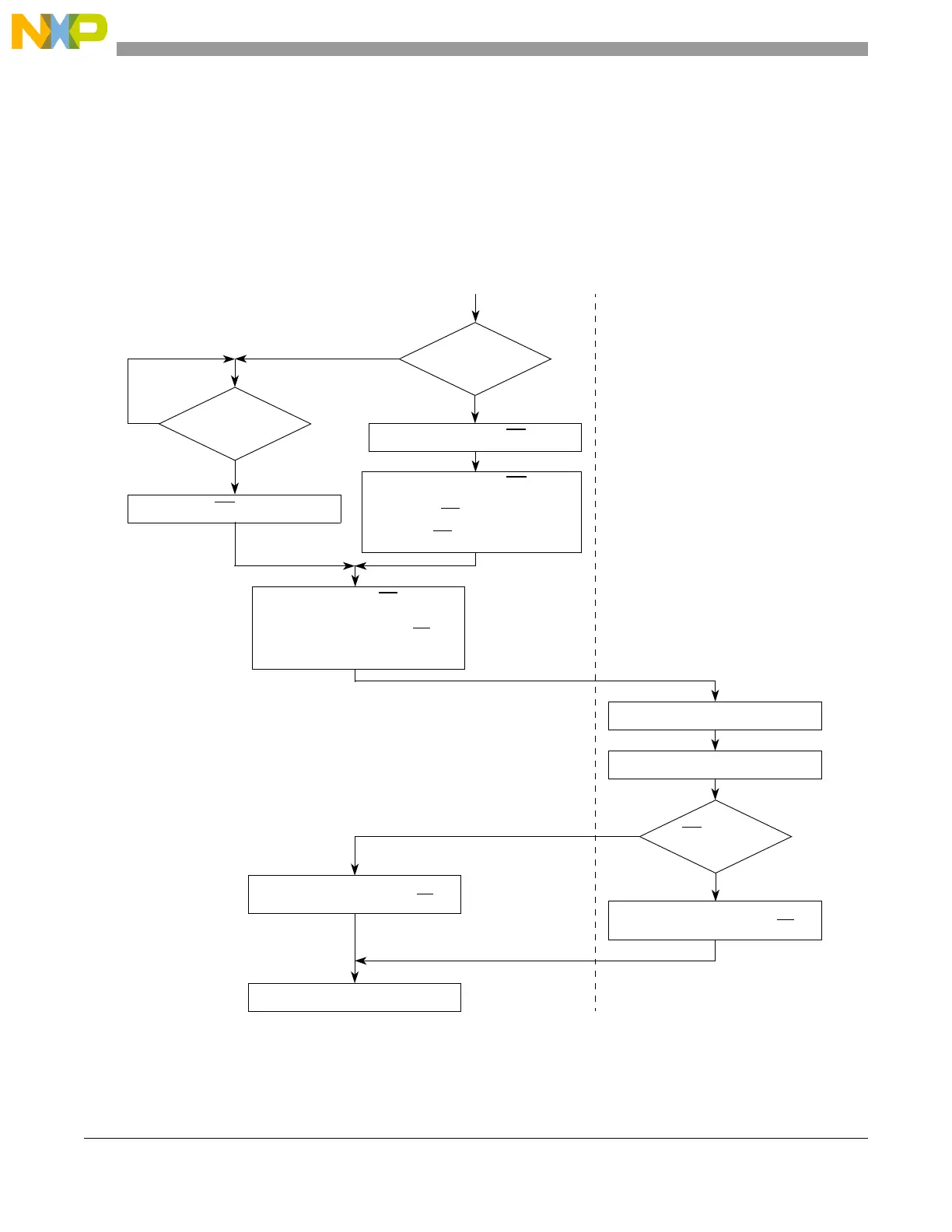

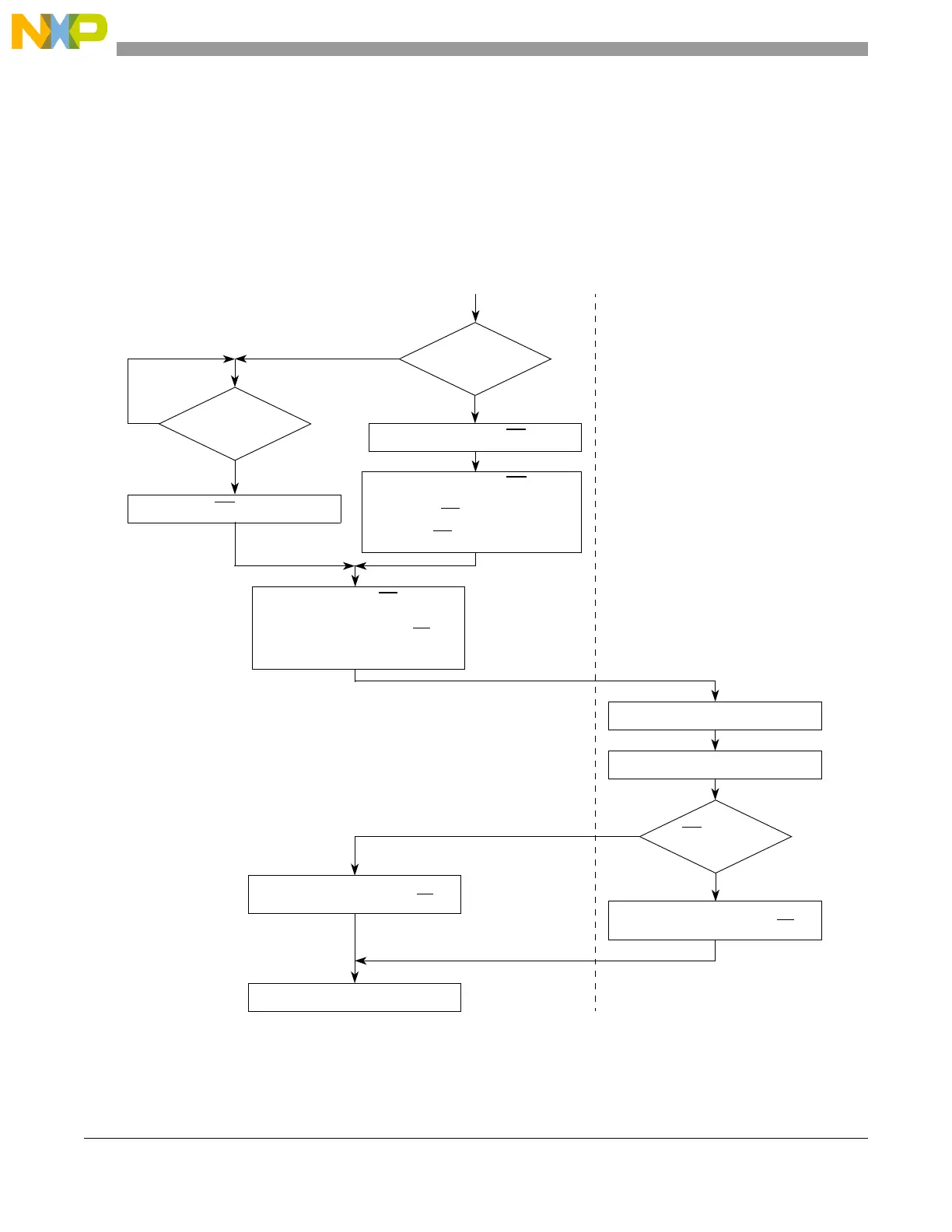

12.4.2.10.3 Bus Transfers Initiated by the EBI in External Master Mode

The flow and timing for EBI-mastered transactions in external master mode is the same as described for

single master mode, except that the EBI arbitrates bus transmissions for each transaction.

The following flow and timing diagrams show the arbitration sequence added to Figure 12-9 and

Figure 12-10 for the basic single-beat read operation. The remaining operations (writes, bursts, etc.) add

the arbitration sequence to the flow and timing diagrams shown for single-master mode. See

Section 12.4.2.4, “Single-Beat Transfer,” and Section 12.4.2.5, “Burst Transfer.”

Figure 12-43. Basic Flow Diagram of an EBI Read Access in External Master Mode

1. Assert bus busy (BB)

2. If no other master is driving,

Asserts transfer start (TS

)

3. Drives address and attributes

Master (EBI) Slave

No

Yes

External

arbitration

?

Request bus (BR)

1. Receive bus grant (BG)

asserted from external arbiter

2. Receive BB

negated

3. Negate BR

if no other requests

No

Yes

EBI

has priority

?

Negate BG if asserted

Receives address

Yes

No

Receives data

Drives data

Asserts

transfer acknowledge (TA

)

Asserts

transfer acknowledge (TA

)

CS

access

?

Loading...

Loading...