Frequency Modulated Phase Locked Loop and System Clocks (FMPLL)

MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 11-7

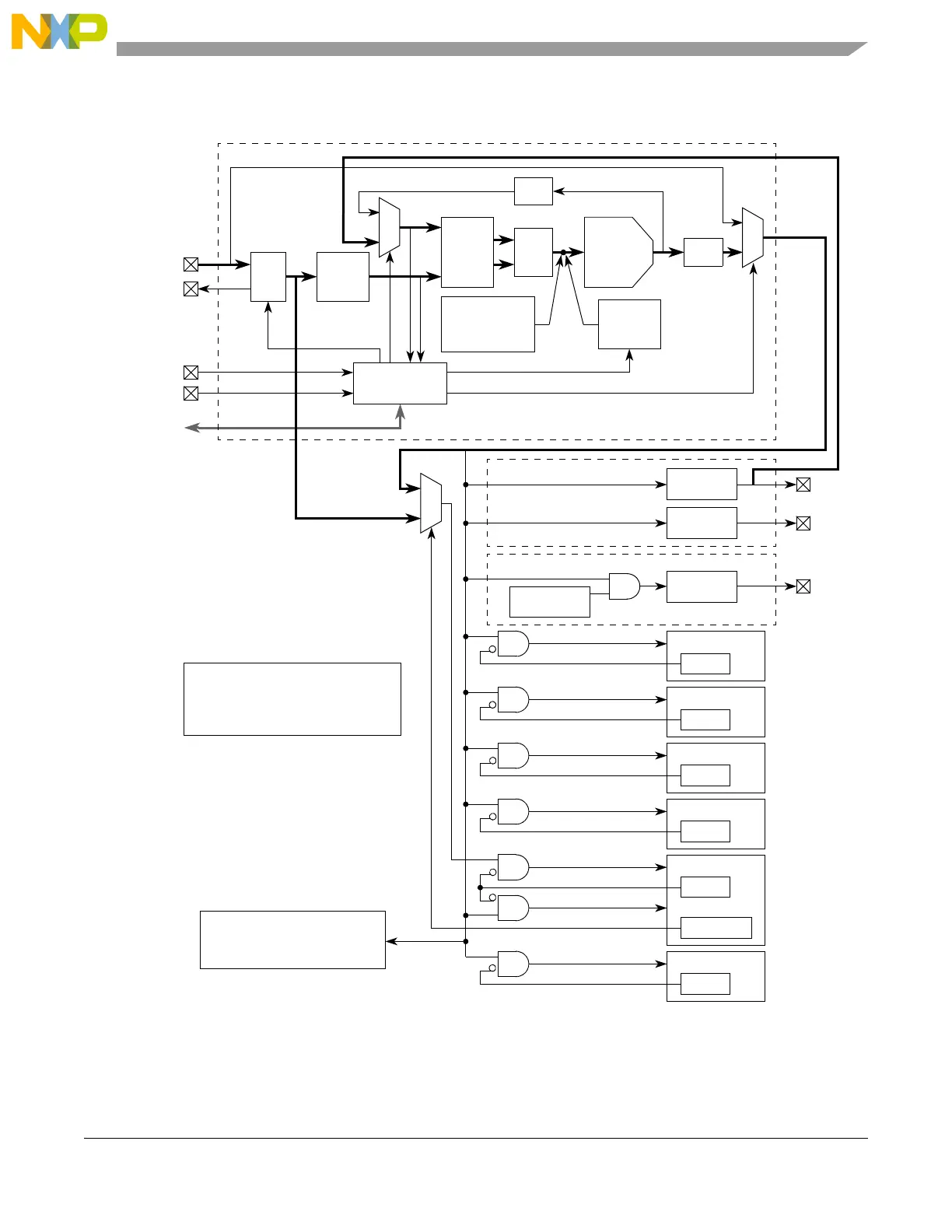

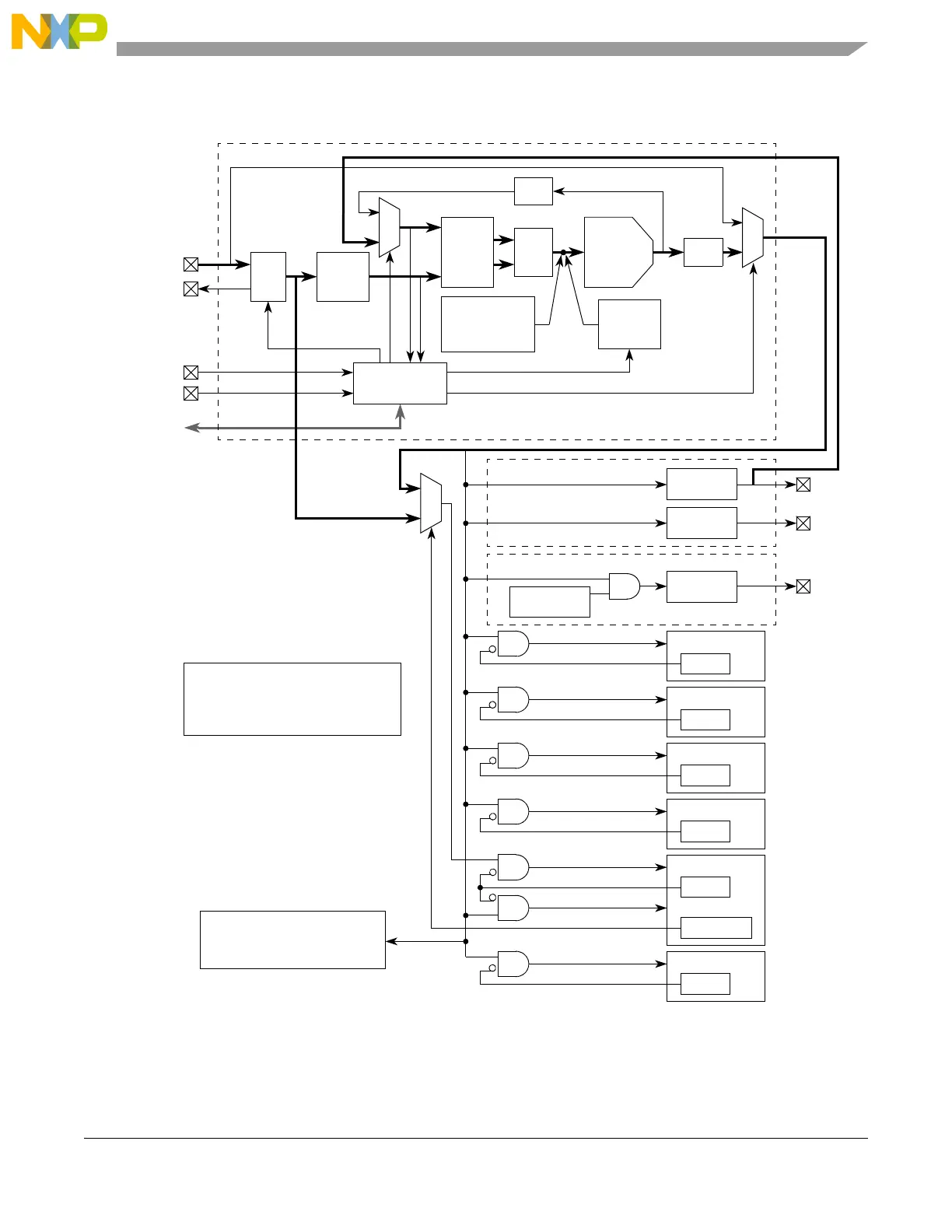

11.1.1.6 FMPLL Dual-Controller Mode (1:1)

Figure 11-6. FMPLL Dual Controller (1:1) Mode

EXTAL_EXTCLK

Bus interface

Control/status

registers

Successive

approximation

frequency

FM

control

XTAL

MFD

PLLCFG[0:1]

MDIS

DSPI

MCKO_EN

MCKO_GT

MCKO

divider

MCKO

MDIS

EBI

MDIS

eMIOS

MDIS

eTPU engines

MDIS

eSCI

MDIS

CAN Interface CLK

FlexCAN

CLK_SRC

Message buffer CLK

ENGCLK

divider

CLKOUT

divider

ENGCLK

CLKOUT

NPC

PLLREF

PLLSEL

MODE

Core, INTC, eDMA, SIU, BAM,

RAMs, eQADC, Flash, XBAR,

PBRIDGE_A, PBRIDGE_B

Oscillator clock

SIU

System

clock

1

0

PLL

NOTE: The clock mode selection

and associated package pin settings

and FMPLL_SYNSR settings are

displayed in Table 11-1.

OSC

0

1

1

0

PREDIV

Filter RFD

Current

controlled

oscillator

(ICO)

PFD/

charge

pumps

Loading...

Loading...