Deserial Serial Peripheral Interface (DSPI)

MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 20-71

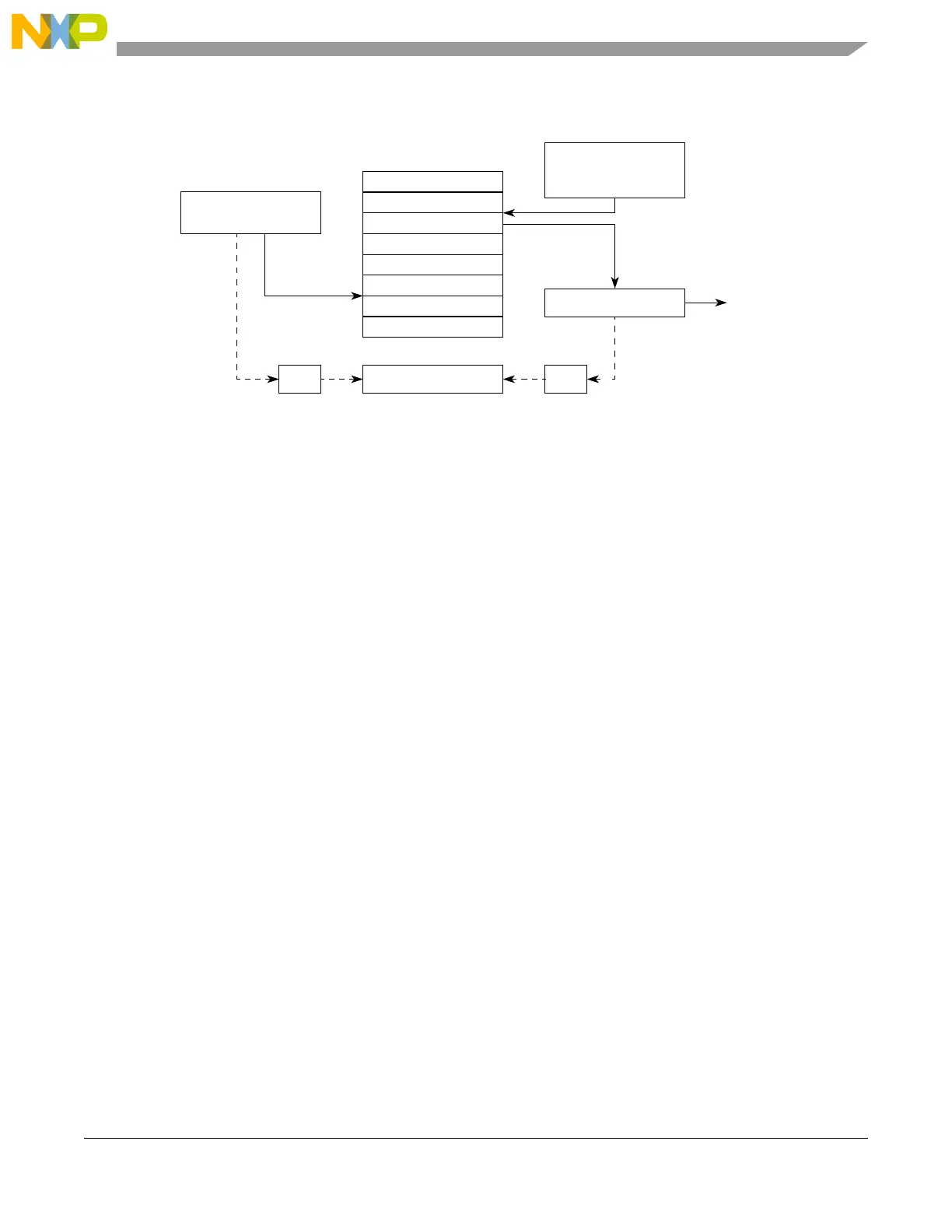

Figure 20-43 illustrates the concept of first-in and last-in FIFO entries along with the FIFO counter.

Figure 20-43. TX FIFO Pointers and Counter

20.5.5.1 Address Calculation for the First-in Entry and Last-in

Entry in the TX FIFO

The memory address of the first-in entry in the TX FIFO is computed by the following equation:

First-in entry address = TXFIFO base + 4 (TXNXTPTR)

The memory address of the last-in entry in the TX FIFO is computed by the following equation:

Last-in entry address = TXFIFO base + (4 x [(TXCTR + TXNXTPTR - 1) modulo TXFIFO depth])

where:

TXFIFO base = base address of transmit FIFO

TXCTR = transmit FIFO counter

TXNXTPTR = transmit next pointer

TX FIFO depth = transmit FIFO depth, implementation specific

20.5.5.2 Address Calculation for the

First-in Entry and Last-in Entry in the RX FIFO

The memory address of the first-in entry in the RX FIFO is computed by the following equation:

First-in entry address = RXFIFO base + 4 x (POPNXTPTR)

The memory address of the last-in entry in the RX FIFO is computed by the following equation:

Last-in entry address = RXFIFO base + 4 x [(RXCTR + POPNXTPTR - 1) modulo RXFIFO depth]

where:

RXFIFO base = base address of receive FIFO

RXCTR = receive FIFO counter

POPNXTPTR = pop next pointer

RX FIFO depth = receive FIFO depth, implementation specific

Entry C

Entry A (first in)

– 1

Entry B

Entry D (last in)

TX FIFO base

Push TX FIFO

TX FIFO counter

Shift register SOUT

register

Transmit next

data pointer

–

–

–

–

+ 1

(TXNXTPTR)

Loading...

Loading...