Deserial Serial Peripheral Interface (DSPI)

MPC5566 Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor 20-41

20.4.4.2 DSI Slave Mode

In DSI slave mode the DSPI responds to transfers initiated by an SPI or DSI bus master. In this mode the

DSPI does not initiate DSI transfers. Certain transfer attributes such as clock polarity and phase must be

set for successful communication with a DSI master. The DSI slave mode transfer attributes are set in the

DSPIx_CTAR1.

If the CID bit in the DSPIx_DSICR is set and the data in the DSPIx_COMPR differs from the selected

source of the serialized data, the slave DSPI asserts the MTRIG signal. If the slave’s internal hardware

trigger signal is asserted and the TRRE is set, the slave DSPI asserts MTRIG. These features are included

to support chaining of several DSPI. Details about the MTRIG signal are found in Section 20.4.4.7,

“Multiple Transfer Operation (MTO).”

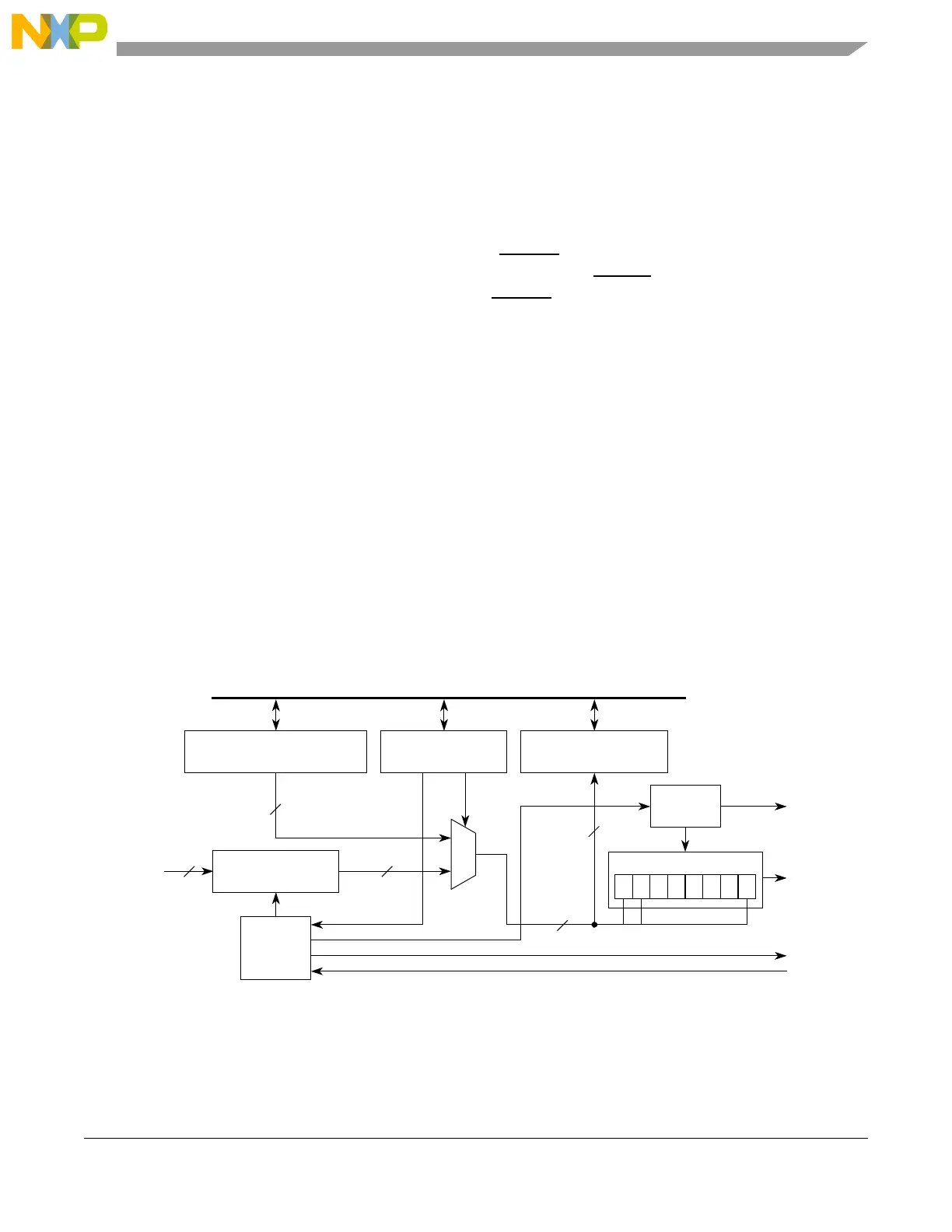

20.4.4.3 DSI Serialization

In the DSI configuration, 4 to 16 bits can be serialized using two different sources. The TXSS bit in the

DSPIx_DSICR selects between the DSPIx_SDR and DSPIx_ASDR as the source of serialized data. See

Section 20.3.2.11, “DSPI DSI Serialization Data Register (DSPIx_SDR),” and Section 20.3.2.12, “DSPI

DSI Alternate Serialization Data Register (DSPIx_ASDR),” for more details. The DSPIx_SDR holds the

latest parallel input signal values which is sampled at every rising edge of the system clock. The

DSPIx_ASDR is written by host software and used as an alternate source of serialized data.

A copy of the last DSI frame shifted out of the shift register is stored in the DSPIx_COMPR. This register

provides added visibility for debugging and it serves as a reference for transfer initiation control.

Section 20.3.2.13, “DSPI DSI Transmit Comparison Register (DSPIx_COMPR),” contains details on the

DSPIx_COMPR.

Figure 20-19 shows the DSI serialization logic.

Figure 20-19. DSI Serialization Diagram

1

0

DSPI alternate

serialization data register

SOUTx

Parallel

DSI configuration

register

DSI transmit

comparison register

Clock

logic

0 1 • • • • • 15

Shift register

DSI serialization

data register

Control

logic

SCKx

inputs

PCSx

ht

16

16

16

16

TXSS

Slave bus interface

16

Loading...

Loading...