Enhanced Queued Analog-to-Digital Converter (eQADC)

MPC5566 Microcontroller Reference Manual, Rev. 2

19-12 Freescale Semiconductor

19.3.2 eQADC Register Descriptions

19.3.2.1 eQADC Module Configuration Register (EQADC_MCR)

The EQADC_MCR contains bits used to control how the eQADC responds to a debug mode entry request,

and to enable the eQADC SSI interface.

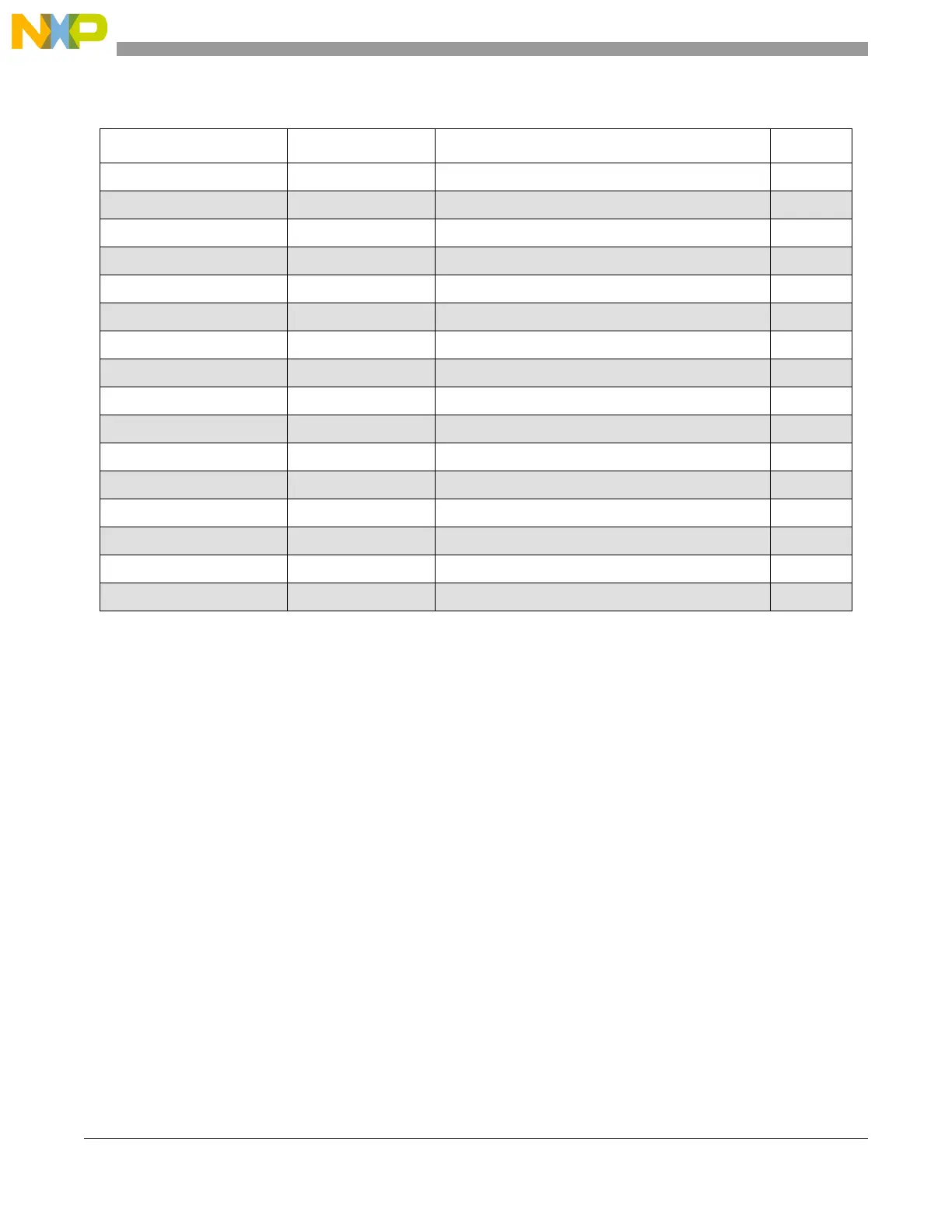

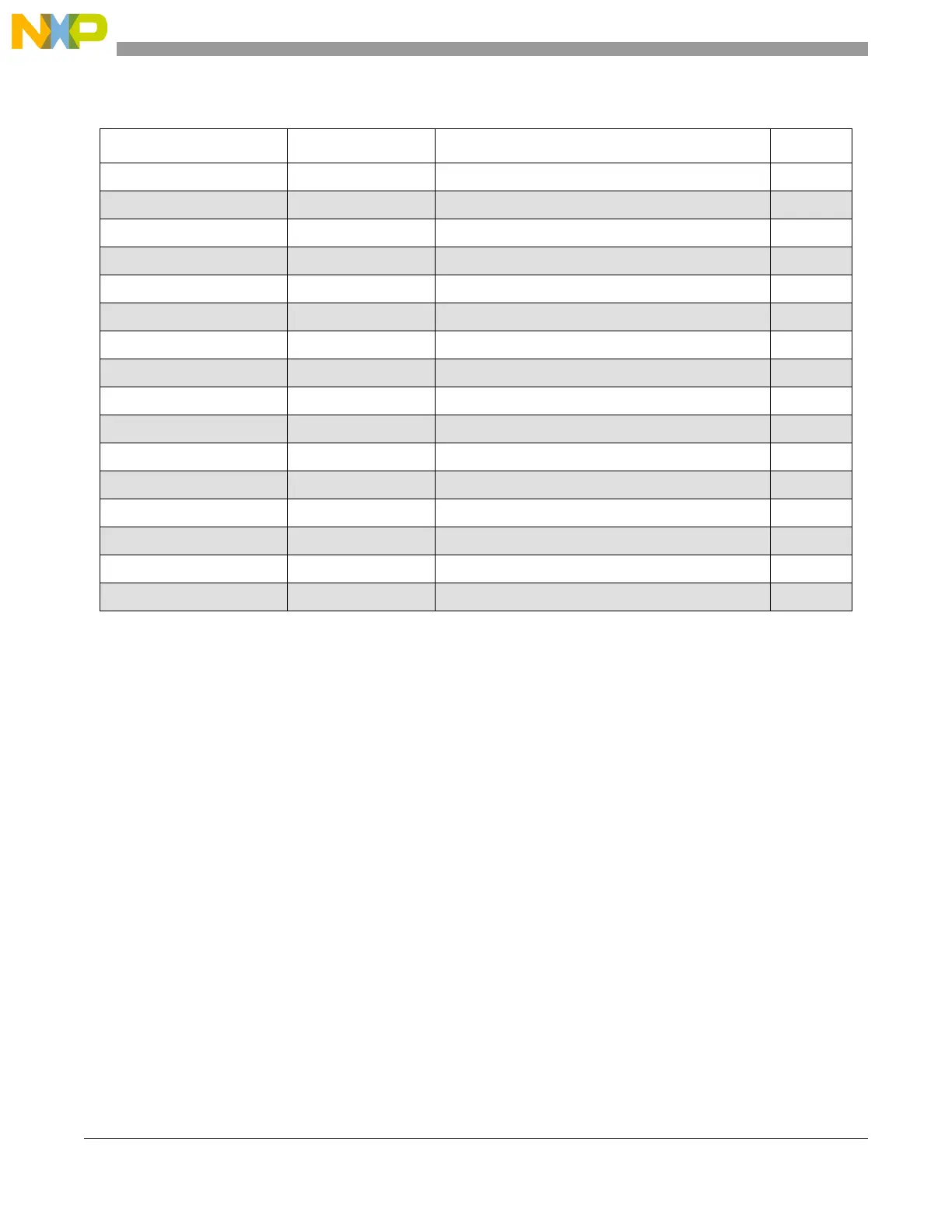

Base + (0x0200–0x020C) EQADC_CF4Rn eQADC CFIFO4 registers 0–3 32

Base + (0x0210–0x023C) — Reserved —

Base + (0x0240–0x024C) EQADC_CF5Rn eQADC CFIFO5 registers 0–3 32

Base + (0x0250–0x02FC) — Reserved —

Base + (0x0300–0x030C) EQADC_RF0Rn eQADC RFIFO0 registers 0–3 32

Base + (0x0310–0x033C) — Reserved —

Base + (0x0340–0x034C) EQADC_RF1Rn eQADC RFIFO1 registers 0–3 32

Base + (0x0350–0x037C) — Reserved —

Base + (0x0380–0x038C) EQADC_RF2Rn eQADC RFIFO2 registers 0–3 32

Base + (0x0390–0x03BC) — Reserved —

Base + (0x03C0–0x03CC) EQADC_RF3Rn eQADC RFIFO3 registers 0–3 32

Base + (0x03D0–0x03FC) — Reserved —

Base + (0x0400–0x040C) EQADC_RF4Rn eQADC RFIFO4 registers 0–3 32

Base + (0x0410–0x043C) — Reserved —

Base + (0x0440–0x044C) EQADC_RF5Rn eQADC RFIFO5 registers 0–3 32

Base + (0x0450–0x07FC) — Reserved —

1

Result FIFOs are 16-bits wide [0:15]; bits [16:31] are filled with zeros to allow for 32-bit read access.

Table 19-2. eQADC Memory Map (continued)

Address Register Name Register Description Bits

Loading...

Loading...