System Integration Unit (SIU)

MPC5566 Microcontroller Reference Manual, Rev. 2

6-122 Freescale Semiconductor

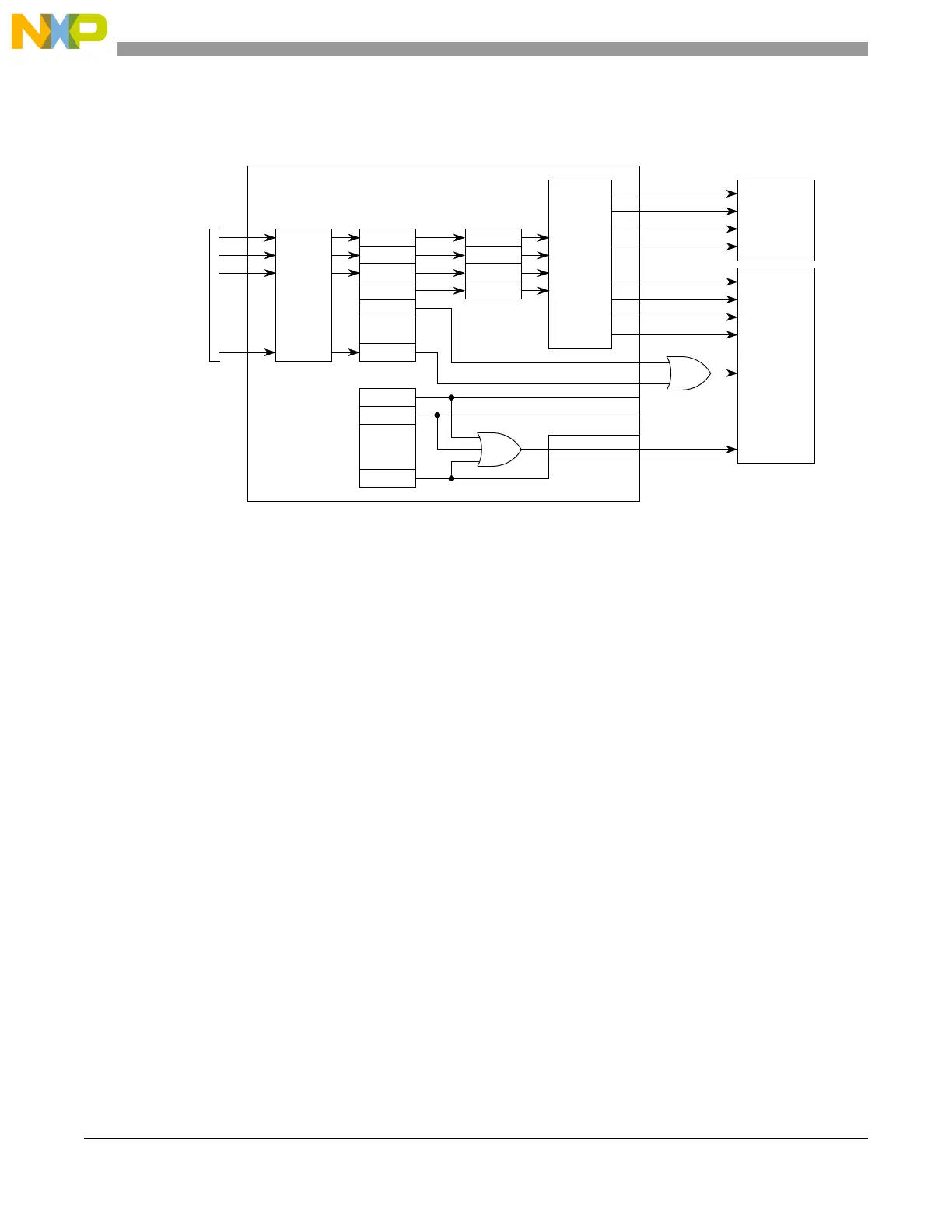

Each IRQ pin has a programmable filter for rejecting glitches on the IRQ signals. The filter length for the

IRQ pins is specified in the external IRQ digital filter register (SIU_IDFR).

Figure 6-170. SIU DMA/Interrupt Request Diagram

6.4.4 GPIO Operation

All GPIO functions for the device are provided by the SIU. Each device pad that has a GPIO signal has a

pin configuration register (PCR) in the SIU where the GPIO function is selected. In addition, each device

GPIO signal has an input data register (SIU_GPDIn) and an output data register (SIU_GPDOn).

6.4.5 Internal Multiplexing

The internal multiplexing select registers (SIU_ETISR, SIU_EIISR, and SIU_DISR) select the input

source for the following components:

• eQADC external trigger input signals

• SIU external interrupt request signals

• DSPI signals used for chaining serial and parallel DSPI modules

Interrupt

controller

DMA/

interrupt

select

•

•

•

•

•

0

1

2

3

4

15

IMUX

Interrupt

request

DMA

request

DMA

•

•

•

0

1

15

SIU_OSR

SIU_EISR

Overrun

request

EIRQ pins

or

internal

source

•

•

•

•

•

•

•

•

•

•

•

•

•

•

Interrupt

request

SIU_DISR

SIU

Loading...

Loading...