Deserial Serial Peripheral Interface (DSPI)

MPC5566 Microcontroller Reference Manual, Rev. 2

20-30 Freescale Semiconductor

20.3.2.11 DSPI DSI Serialization Data Register (DSPIx_SDR)

The DSPIx_SDR contains the signal states of the parallel input signals from the eTPU or the eMIOS. The

pin states of the parallel input signals are latched into the DSPIx_SDR on the rising edge of every system

clock. The DSPIx_SDR is read-only. When the TXSS bit in the DSPIx_DSICR is negated, the data in the

DSPIx_SDR is the source of the serialized data.

The following table describes the field in the DSPI deserial serial interface serialization data register:

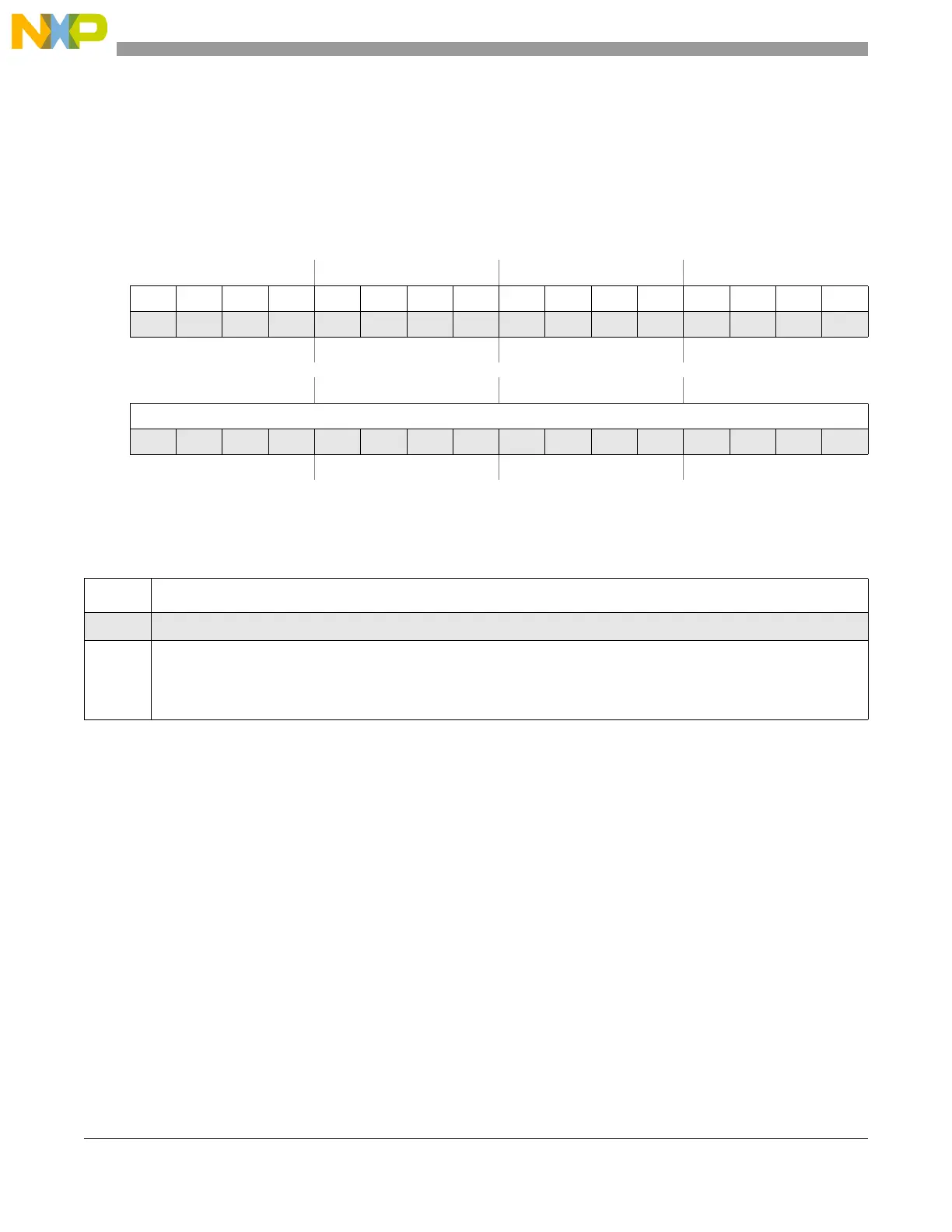

Address: Base + 0x00C0 Access: R/O

0123456789101112131415

R0000000000000000

W

Reset0000000000000000

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R SER_DATA [15:0]

W

Reset0000000000000000

Figure 20-13. DSPI DSI Serialization Data Register (DSPIx_SDR)

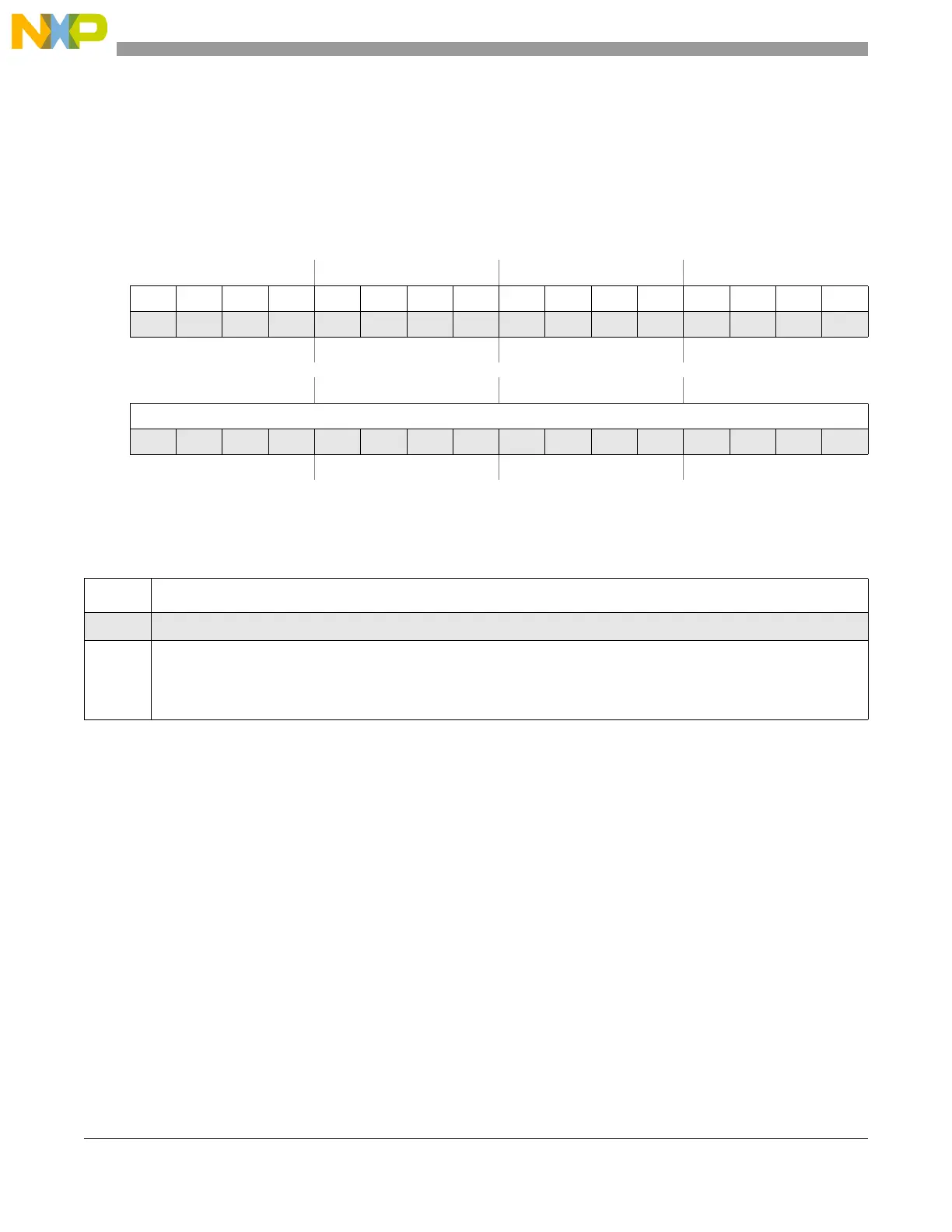

Table 20-13. DSPIx_SDR Field Description

Bits Description

0–15 Reserved

16–31

SER_

DATA

[15:0]

Serialized data. The SER_DATA field contains the signal states of the parallel input signals. SER_DATA [15:0] maps

to DSPI serialization inputs IN[15:0]. See Section 20.4.4.6, “DSPI Connections to eTPUA, eTPUB, eMIOS and SIU.”

Loading...

Loading...