TC1796

System Units (Vol. 1 of 2)

CPU Subsystem

User’s Manual 2-3 V2.0, 2007-07

CPU, V2.0

• Optional Memory Management instruction set not implemented

(Memory management configuration registers are always read as MMU not present)

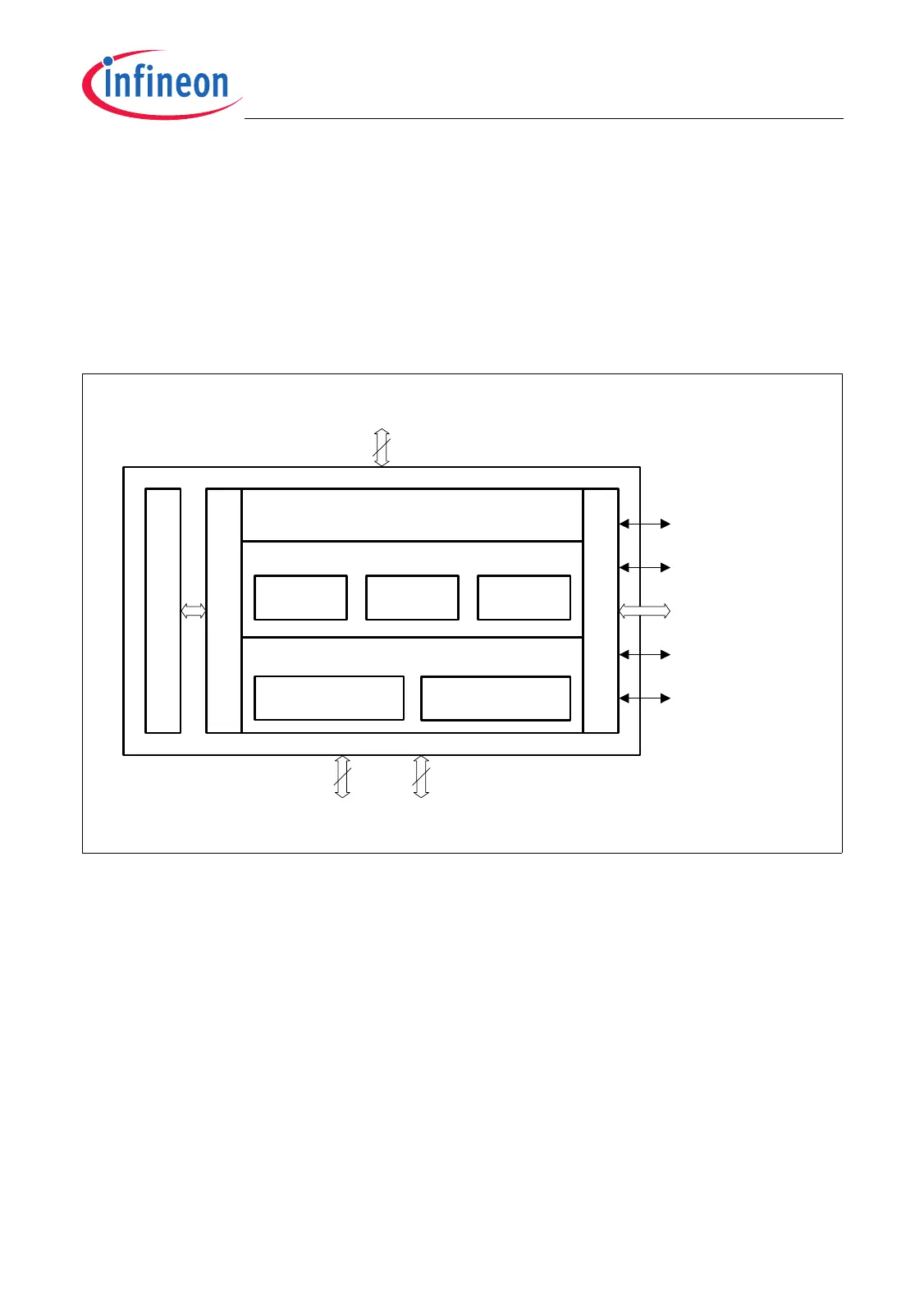

2.2.1 CPU Diagram

The Central Processing Unit (CPU) is comprised of an Instruction Fetch Unit, an

Execution Unit, a General Purpose Register File (GPR), a CPU Slave interface (CPS),

and optional Floating Point Unit (FPU).

Figure 2-2 CPU Block Diagram

Execution Unit

MCB05586

To Program Memory Interface (PMI)

Integer

Pipeline

General Purpose Register File (GPR)

Instruction Fetch Unit

Core Register

Access

Address Registers Data Registers

To Data Memory Interface (DMI)

64

Coprocessor Interface

Floating Point Unit (FPU)

CPU Slave Interface (CPS)

Interrupts

System Control

Test

Debug/Emulation

Loop

Pipeline

Load Store

Pipeline

64

64

Loading...

Loading...