TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-82 V2.0, 2007-07

EBU, V2.0

13.10.2 Clock Control Register, CLC

Note: While the DISR bit is implemented in the EBU, a request to disable the module will

be ignored. This register is Endinit-protected after initialization. Writing to this

register in this state will cause the EBU to generate an LMB Error.

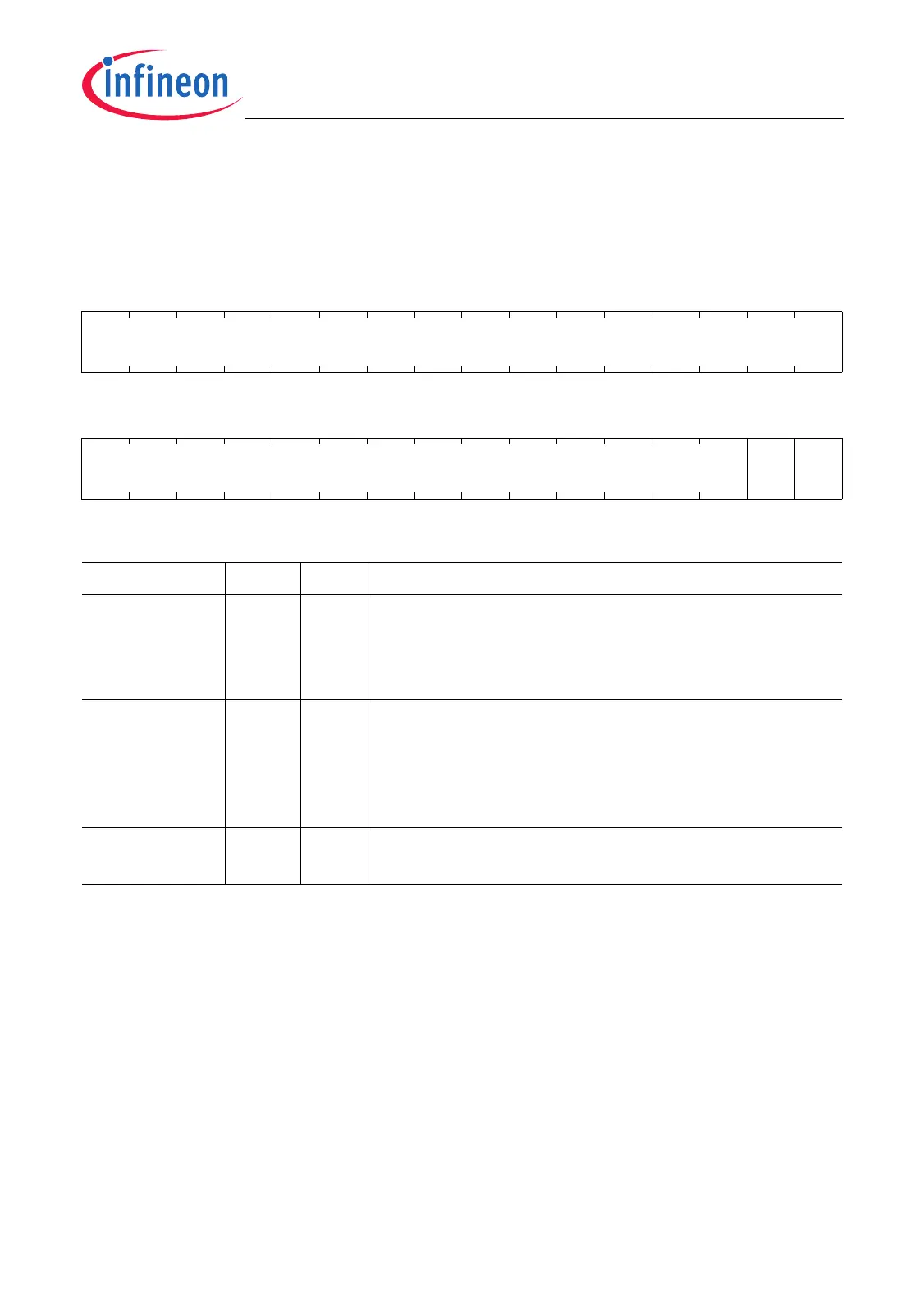

EBU_CLC

EBU Clock Control Register (000

H

) Reset Value: 0000 0000

H

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0 DISS DISR

rrrw

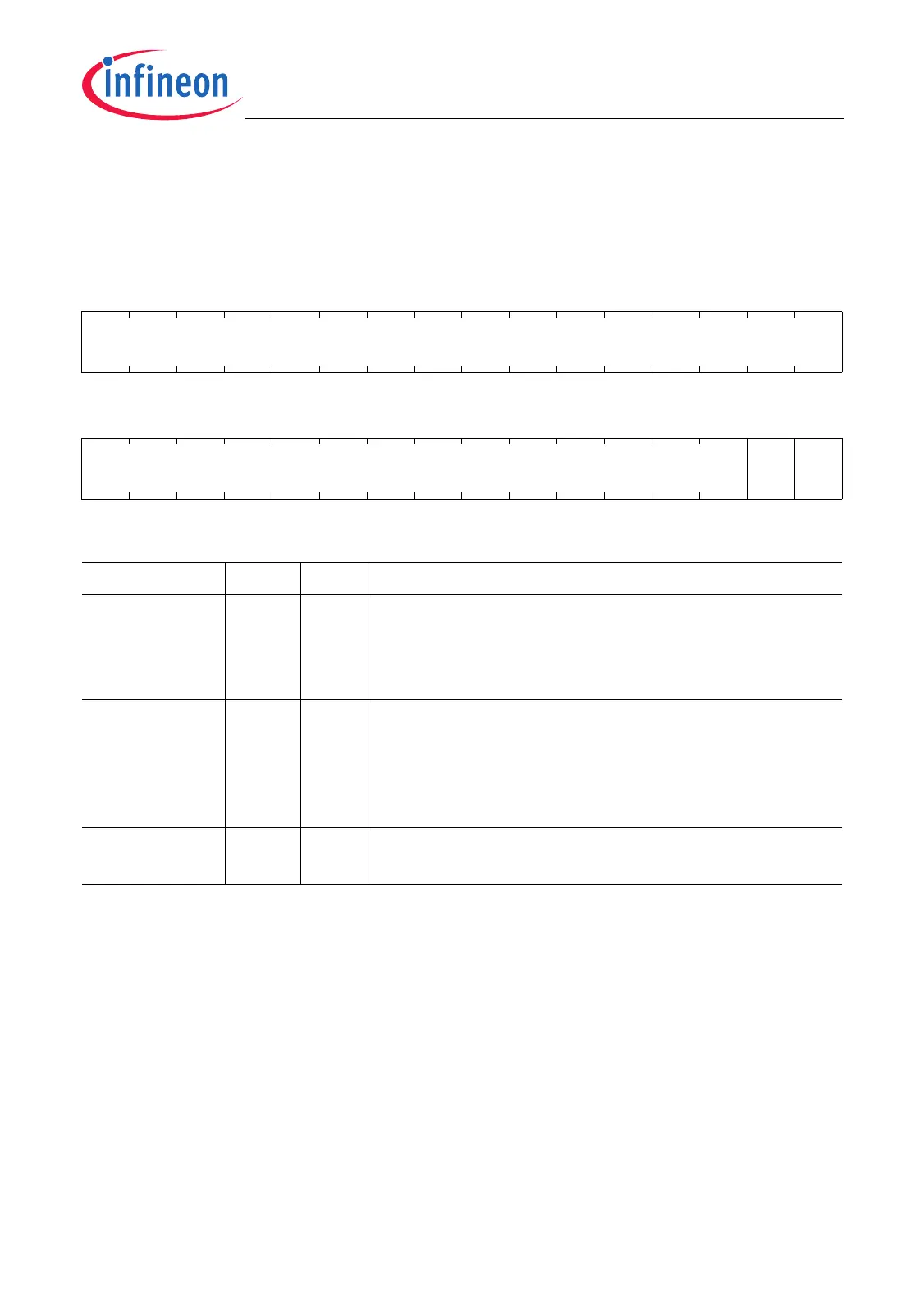

Field Bits Type Description

DISR 0rwEBU Disable Request Bit

This bit is used for enable/disable control of the EBU.

0

B

EBU disable is not requested

1

B

EBU disable is requested

DISS 1rEBU Disable Status Bit

0

B

EBU is enabled (default after reset)

1

B

EBU is disabled

In the TC1796, DISS is always read as 0, meaning

that the EBU is always enabled.

0 [31:2] r Reserved

Read as 0; should be written with 0.

Loading...

Loading...