TC1796

System Units (Vol. 1 of 2)

General Purpose I/O Ports and Peripheral I/O Lines

User’s Manual 10-25 V2.0, 2007-07

Ports, V2.0

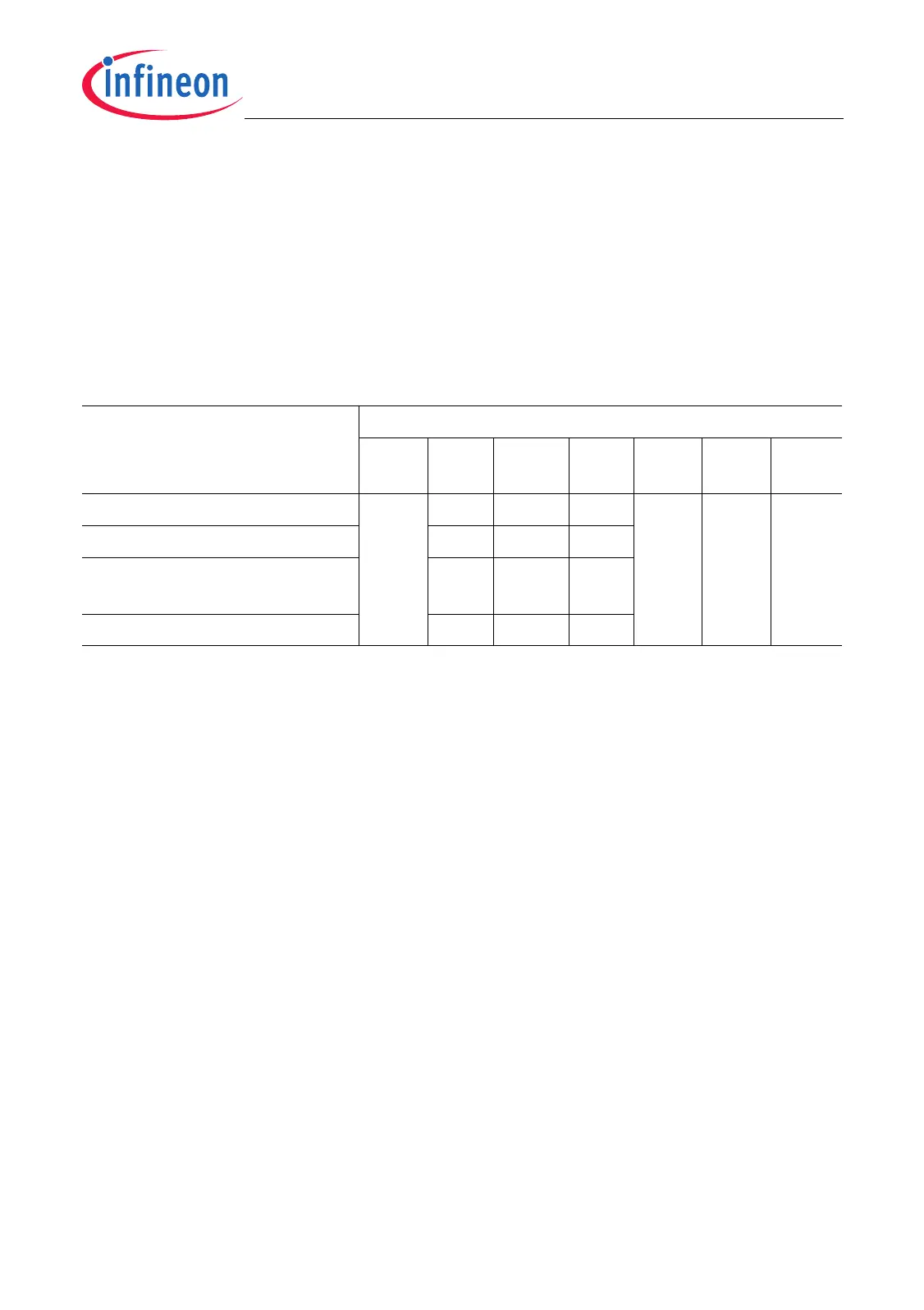

10.3.3.3 Reserved SWOPT Bits of SCU_SCLIR Register

Depending on the TC1796 device version used in an application, several Port 0 lines

(meaning several SWOPT bits) are reserved and cannot be used for user system

purposes during a HDRST reset operation. Table 10-8 defines the reserved Port 0 lines

(indicated by 0 or 1) as well as the Port 0 lines that can be used by a user program

(indicated by “user”) for software configuration selection (or as GPIO pins) depending on

the specific TC1796 device version.

Table 10-8 Reserved SWOPT Bits in TC1796 Devices

TC1796 Device Version SWOPTx Bits (x = 0-15)

P0.

[15:8]

P0.

[7:6]

P0.5 P0.4 P0.3 P0.

[2:0]

P0.

[15:8]

TC1796 user user user 1 user

1)

1) The P0.[2:0] bits are only used in alternate boot modes (see Page 4-28). If alternate boot modes are not

required or used in an application, P0.[2:0] can also be used for user program software configuration selection

purposes during a hardware reset operation or as GPIO pins.

user

TC1796ED (Emulation device) user 0 or 1

2)

2) 0: Emulation device functionality is not available.

1: Emulation device functionality is fully supported.

1

TC1796-L

(Flash-Not-Available version)

user 11B

3)

3) In Flash-Not-Available devices/sockets with P0.4 = 0, P0.[7:6] are used for test purposes and must always be

set to 11

B

during a hardware reset operation.

0

TC1796ED in TC1796-L socket 11

B

3)

0 or 1

2)

0

Loading...

Loading...