TC1796

System Units (Vol. 1 of 2)

LMB External Bus Unit

User’s Manual 13-38 V2.0, 2007-07

EBU, V2.0

• During an access to a 16-bit wide external region, either Buffer 1 or Buffer 2 is

enabled (according to bit 2 of the PLMB address being accessed) and either Buffer 4

or Buffer 5 is enabled (according to bit 1 of the PLMB address being accessed). This

allows any PLMB channel byte pair (i.e. any properly aligned 16-bit data) to be re-

aligned to the lower 16 bits of the external data bus D[15:0].

Note: When accessing a 16-bit wide external region programmed for big-endian

operation, the PLMB address is modified prior to being driven to the external bus

(see Table 13-13 on Page 13-36). For a 64-bit access, this will generate external

bus accesses in the address sequence X010

B

, X000

B

, X110

B

, X100

B

. For a 32-bit

access, the external bus address sequence will be XX10

B

, XX00

B

.

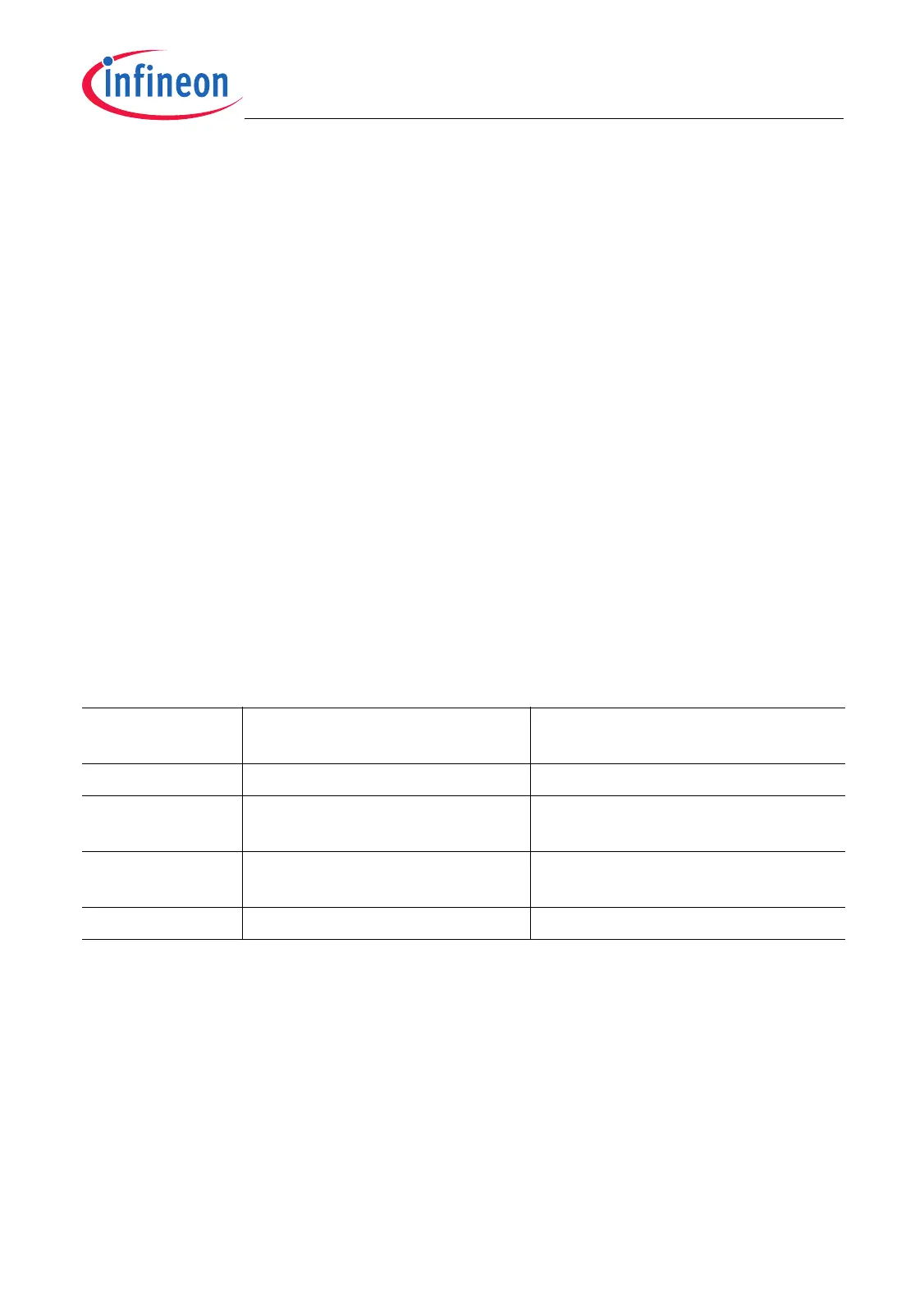

13.5.7 Address Alignment During Bus Accesses

During an external bus access, the EBU will optionally align the internal byte address to

generate the appropriate external word or half-word address aligned to the external

address pins A[23:0]. This address alignment is enabled separately for each region by

the AALIGN bit in the EBU_BUSCONx or EBU_EMUBC registers. When enabled,

alignment will be performed according to the selected bus width (i.e. the value of the

appropriate PORTW bit field in the EBU_BUSCONx or EBU_EMUBC registers). The

address alignment will be done as defined in Table 13-14.

When alignment is not enabled (default after reset) for a region, the EBU will issue a byte

address to the external bus.

Table 13-14 EBU External Bus Address Alignment

Parameter

PORTW

Selected Bus Width Address Alignment

00

B

Reserved –

01

B

16-bit External address A[23:0] =

PLMB address [24:1]

10

B

32-bit External address A[23:0] =

PLMB address [25:2]

11

B

Reserved –

Loading...

Loading...