TC1796

System Units (Vol. 1 of 2)

Clock System and Control

User’s Manual 3-8 V2.0, 2007-07

Clock, V2.0

3.2.1.4 Oscillator Control Register

Note: Register OSC_CON is Endinit-protected.

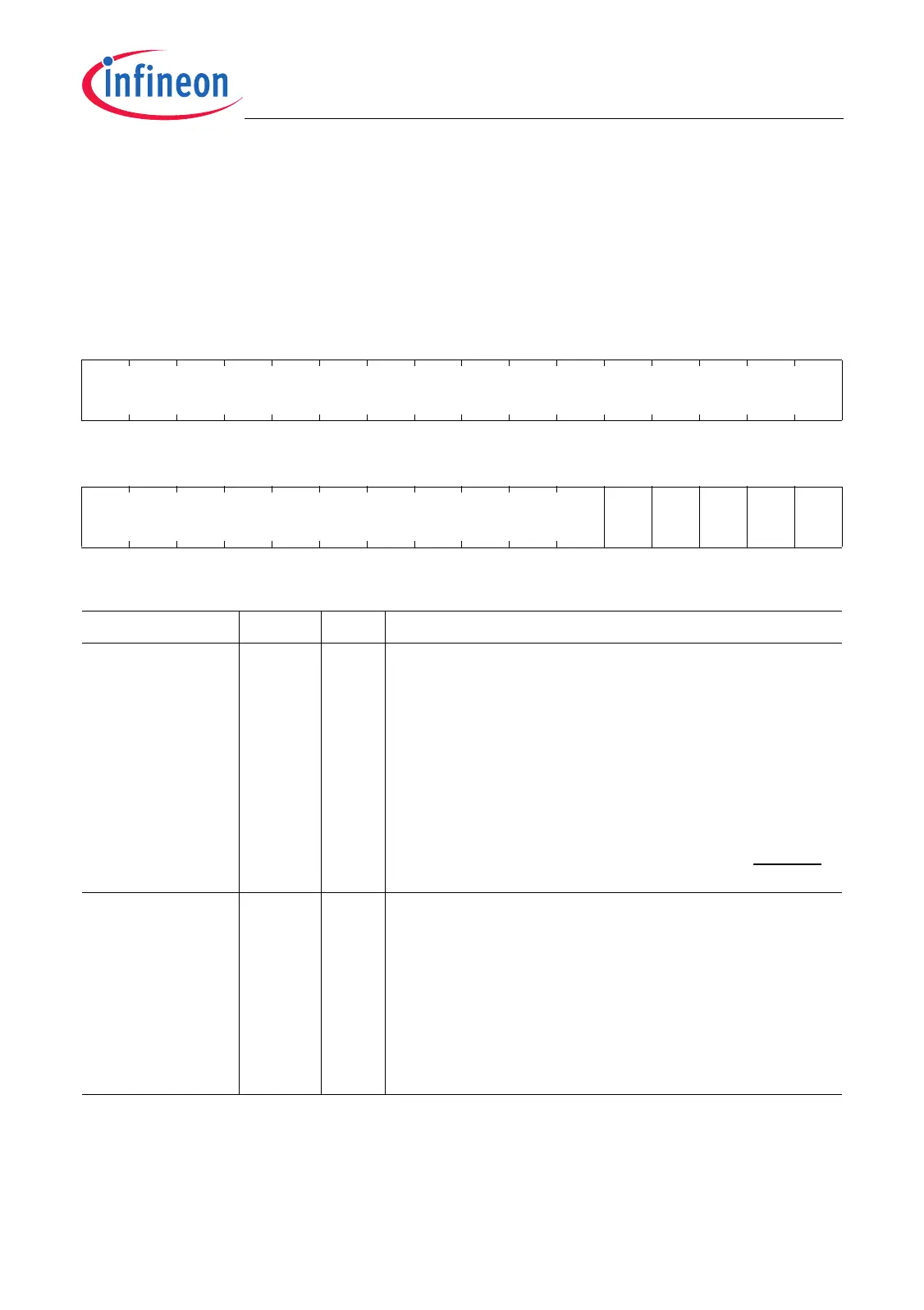

OSC_CON

Oscillator Control Register (F0000018

H

) Reset Value: see Table 3-1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

0

r

1514131211109876543210

0OGC0

ORD

RES

OSC

R

MOS

C

rrwrrwhrhrwh

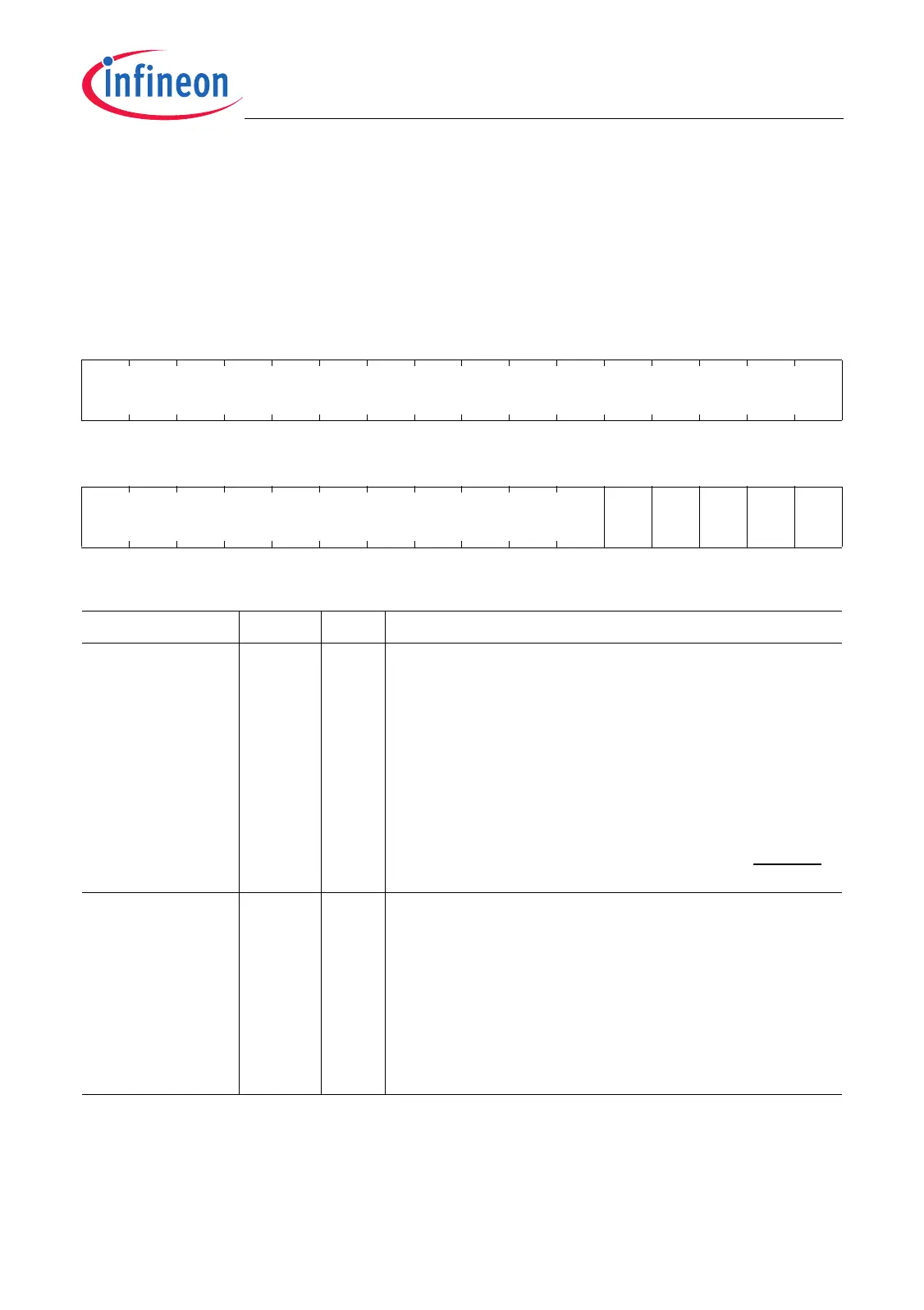

Field Bits Type Description

MOSC 0rwhMain Oscillator Test Mode

This bit determines the mode of the main oscillator.

0

B

The oscillator is running. The oscillator signal

of the main oscillator or an external clock

input signal is used as f

OSC

.

1

B

The oscillator circuitry is bypassed. An

external clock input signal at XTAL1 must be

provided and is used as f

OSC

.

It is 1 if the BYPASS pin is high and TXD1A is zero.

Its state is latched with the rising edge of PORST.

OSCR 1rhOscillator Run Status Bit

This bit shows the state of the oscillator run state.

0

B

The oscillator is not running.

1

B

The oscillator is running.

The OSCR bit is valid always after a power-on reset

operation. After an oscillator run detection reset

(setting OSC_CON.ORDRES), OSCR is invalid up

to a maximum of 64 f

N

clock cycles.

Loading...

Loading...